【導讀】DDR3主控為國外知名公司的芯片,按說該芯片的常規(guī)設計對于我們的設計人員來說應該沒有太大的問題,但是,這個設計的硬件工程師出于后期調(diào)試和EMI的考慮在所有的數(shù)據(jù)信號線上加了串阻,這就使得原本就很緊張的布線空間捉襟見肘了,為此我們的設計人員叫苦不迭,這么緊張的空間怎么去繞等長呢?

話說有三個人將被依次執(zhí)行死刑,分別是牧師、律師、工程師。

牧師第一個被推向絞刑架。儈子手拉動控制桿以抽出活板,但它失靈了。牧師宣稱這是上帝的旨意,要求得到釋放,于是他獲得了自由。

接著,律師走向了絞刑架。儈子手再一次拉動了控制桿,但它仍然失靈,律師同樣要求獲得釋放,因為他不能因為同一罪狀被判兩次死刑,于是他也獲得了自由。

最后,輪到工程師了。他上去對腳手架仔細檢查了一遍,在儈子手還沒動手之前,他抬起頭大聲說,“啊哈,是這里出了故障!”

看到這里,大家應該知道結(jié)果了吧,真是好奇害死貓,有時工程師的強迫癥來了真的會差點累及無辜。

這不,最近就遇到了一件很揪心的DDR3設計。

該DDR3主控為國外知名公司的芯片,功能強大而且比較成熟了,該設計為32位系統(tǒng),一個主控芯片拖了4片DDR3顆粒,采用6層板,空間比較緊張。這種常規(guī)設計對于我們的設計人員來說應該沒有太大的問題,好歹我們一年也有好幾千款的DDRx設計,在這個上面的技術積累還是很多的。但是,這個設計的硬件工程師出于后期調(diào)試和EMI的考慮在所有的數(shù)據(jù)信號線上加了串阻,這就使得原本就很緊張的布線空間捉襟見肘了,為此我們的設計人員叫苦不迭,這么緊張的空間怎么去繞等長呢?就算累到?jīng)]朋友恐怕也很難保證很好的完成設計吧!無解了,只能請高速先生出招!

首先查看了下主控芯片的數(shù)據(jù)手冊,什么ODT、Write leveling該有的功能都有,好家伙,這下有救了。為什么呢?因為我們有任性的ODT功能。

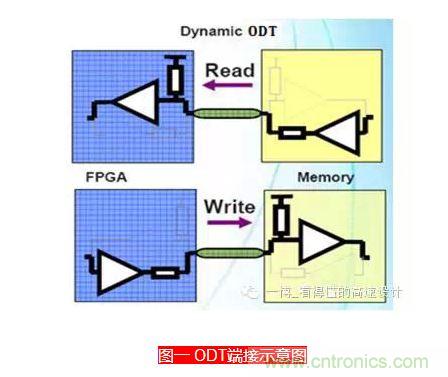

ODT是On Die Termination的縮寫,又叫片內(nèi)端接,顧名思義,就是將端接電阻放在了芯片內(nèi)部,這個功能只有在DDR2以上的數(shù)據(jù)信號才有,其他信號無此寵幸!有了這個功能,原本需要在PCB板上加串阻的數(shù)據(jù)信號就不用再額外添加端接了,因為芯片內(nèi)部可以打開這個ODT端接功能,而且端接還可調(diào),哈哈,確實有點任性。下面是ODT的端接示意圖。

當數(shù)據(jù)讀操作的時候,主控(FPGA或CPU)讀取Memory顆粒的數(shù)據(jù),此時主控為接收端,可以根據(jù)需要選擇是否打開ODT;當數(shù)據(jù)寫操作的時候,主控(FPGA或CPU)將數(shù)據(jù)寫入到Memory顆粒,此時顆粒為接收端,也可以根據(jù)需要選擇是否打開ODT,這種操作可以在寄存器內(nèi)部實現(xiàn)控制。

現(xiàn)在回到我們前面的設計,這個數(shù)據(jù)串阻到底有沒有必要呢?答案當然是非必要的,而且可以說是費力不討好(針對此項目)!這也不能怪我們的硬件工程師,既要保證產(chǎn)品性能,又要保證產(chǎn)品有問題的時候多種調(diào)試手段,壓力大,強迫癥就這樣來了!

那又為什么說費力不討好呢?主要有下面兩點:

其一是影響了布線空間,讓寸土寸金的空間雪上加霜,犧牲了走線空間,線間距就很難保證,間接的導致串擾,減少系統(tǒng)裕量;

其二是這個端接已經(jīng)在芯片內(nèi)部有了,再額外在板上加串阻會增加器件成本,同時串阻的位置也有待斟酌,是加在主控端好呢還是加在Memory顆粒端好呢?確實有點畫蛇添足的趕腳!為了后期的好調(diào)試而帶來其他的隱患,得不償失啊!

最后和硬件工程師進行了利害關系溝通后,終于同意去掉數(shù)據(jù)信號的串阻,現(xiàn)在板子已經(jīng)調(diào)試成功,準備量產(chǎn)階段 。