【導(dǎo)讀】器件緩沖似乎是處理開關(guān)過沖、振鈴和損耗的一種“野蠻”解決方案,而這對于諸如IGBT之類較老的技術(shù)來說確實(shí)如此。但是,寬禁帶器件,尤其是SiC FET,可以將該技術(shù)用為柵極電阻調(diào)諧的優(yōu)良替代方案,以提供較低的總損耗。

器件緩沖似乎是處理開關(guān)過沖、振鈴和損耗的一種“野蠻”解決方案,而這對于諸如IGBT之類較老的技術(shù)來說確實(shí)如此。但是,寬禁帶器件,尤其是SiC FET,可以將該技術(shù)用為柵極電阻調(diào)諧的優(yōu)良替代方案,以提供較低的總損耗。

在這個(gè)寬禁帶半導(dǎo)體開關(guān)的新時(shí)代,器件的類型選擇包括SiC MOSFET和GaN高電子遷移率晶體管(HEMT),它們都有自己特性并都聲稱擁有最佳的性能。但是,這兩種都還不是理想的開關(guān),這兩種類型的器件都在某些方面有局限性,特別是在柵極驅(qū)動要求方面和“第三象限”操作方面。

SiC FET提供了另一種選擇

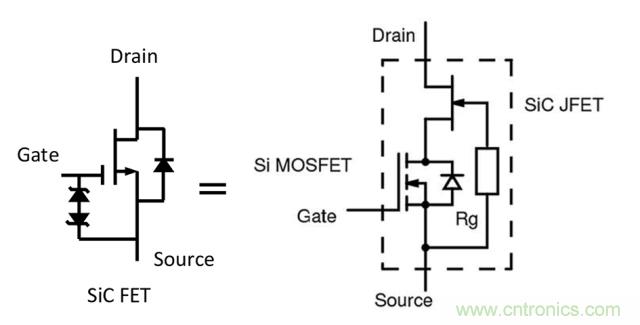

但我們還有另一種選擇。 UnitedSiC FET是SiC JFET和低壓Si MOSFET的一種級聯(lián)組合,具有SiC的速度優(yōu)勢,以及SiC最低傳導(dǎo)損耗的優(yōu)點(diǎn),并且僅需要一個(gè)簡單的柵極驅(qū)動和一個(gè)快速、低功耗的體二極管用于第三象限傳導(dǎo)(圖1)。

圖1:SiC FET — SiC JFET和Si MOSFET的級聯(lián)組合。

SiC FET的速度非???,其邊沿速率為50V/ns甚至更高,這對于最大程度降低開關(guān)損耗非常有用,但所產(chǎn)生的di/dt比值可達(dá)數(shù)安培/納秒。通過封裝和電路電感,這會產(chǎn)生極高的電壓過沖并導(dǎo)致隨后的電壓振鈴現(xiàn)象。在這種電流變化速率下,可簡單分析得出,即使幾十納亨(nH)也可能產(chǎn)生數(shù)百伏的過沖(從公式E = –L(di/dt)得出)。對于快速切換的寬禁帶器件,將這種雜散電感降至最低至關(guān)重要。但是,這在實(shí)際的布線中卻很難實(shí)現(xiàn),因?yàn)椴季€要求必須在高壓組件之間保留安全距離,并且為了獲得更好的熱性能需要使用更大的半導(dǎo)體封裝。

過沖有超過器件額定電壓的風(fēng)險(xiǎn),并給元器件的長期使用增添了壓力,但是快速變換的邊緣也會引起絕緣擊穿,并會產(chǎn)生更多的EMI,導(dǎo)致需要使用更大、更昂貴且損耗更高的濾波器。因此,實(shí)際電路通常會故意降低此類快速開關(guān)的邊沿速率,從而允許使用可能具有更低傳導(dǎo)損耗和更小濾波器的低壓器件,用來抵消稍高的開關(guān)損耗。

緩慢的開關(guān)邊沿可減少過沖和EMI

有兩種常見的減慢開關(guān)邊沿速率的方法:通過增添柵極電阻和通過在器件的漏極-源極端之間使用一個(gè)緩沖器。

增加?xùn)艠O電阻確實(shí)會降低dV/dt,從而減少過沖,但是對漏極電壓隨后出現(xiàn)的振鈴現(xiàn)象幾乎沒有影響。柵極電阻的減慢效果取決于器件的總柵極電荷,而電荷又取決于諸如柵極-源極電容和“米勒”效應(yīng)等的參數(shù)。當(dāng)器件切換時(shí),這些參數(shù)會表現(xiàn)為可變的柵極-漏極電容。導(dǎo)通和關(guān)斷的延遲可以分別通過使用兩個(gè)帶控向二極管的柵極電阻來控制,但是,想要在所有工作條件下都達(dá)到這種總體優(yōu)化的效果是有難度的。此外,增加?xùn)艠O電阻會給柵極驅(qū)動波形帶來延遲,這在高頻應(yīng)用中會是個(gè)大問題。

相反,簡單的Rs-Cs緩沖器可通過增加開關(guān)的漏極電容來減慢dV/dt。它還有一個(gè)額外的效果:由于一些電流需要用來給Cs充電,因此器件關(guān)斷時(shí)電壓上升和電流下降之間的重疊會減少,從而降低了器件的開關(guān)損耗。開關(guān)導(dǎo)通時(shí),必須限制電容器的放電電流,因此要串聯(lián)一個(gè)電阻,當(dāng)器件關(guān)斷時(shí),該電阻還可以抑制振鈴。缺點(diǎn)是電阻器在此過程中不可避免地會消耗一些功率,并且半導(dǎo)體開關(guān)效率的增益會在一定程度上會被抵消。

緩沖器可以成為更低損耗的解決方案

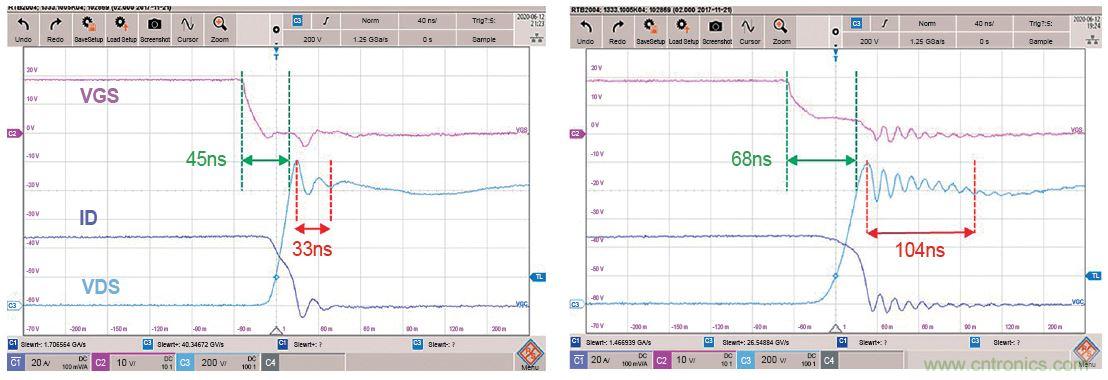

SiC FET技術(shù)開發(fā)商UnitedSiC的研究表明,與單單增加?xùn)艠O電阻相比,僅需一個(gè)非常小的緩沖電容和一個(gè)相應(yīng)的低功率電阻即可實(shí)現(xiàn)對dV/dt、過沖和振鈴更有效的控制。當(dāng)小型緩沖器件與較低的Rg結(jié)合使用時(shí),會產(chǎn)生更低的總損耗和更清晰的波形。這種方法對UnitedSiC的FET和傳統(tǒng)的SiC MOSFET都適用。圖2比較了一個(gè)有200 pF/10Ω緩沖器的器件(左)和一個(gè)添加了5Ω柵極電阻的器件(右)的振鈴現(xiàn)象和dV/dt。雖然兩種方法在關(guān)斷時(shí)都差不多調(diào)諧到了相同的 峰值,但有緩沖器的版本明顯有著更短的延遲時(shí)間和更好的振鈴阻尼。

圖2:使用RC器件緩沖可降低dV/dt,ID/重疊以及SiC MOSFET的振鈴。(ID = 50 A,V = 800 V,TO247-4L;左:SiC MOSFET的關(guān)斷波形,Rg.off = 0Ω,Rs = 10Ω,Cs = 200 pF;右:SiC MOSFET的關(guān)斷波形,Rg.off = 5Ω,無器件緩沖)。

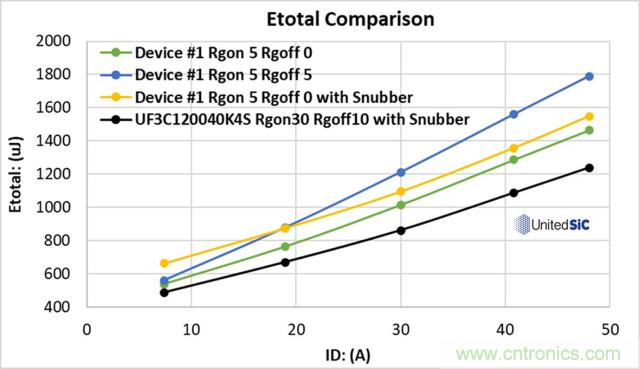

總損耗包含傳導(dǎo)損耗、上升和下降沿上的開關(guān)損耗,以及緩沖電阻中的任何功率消耗。通過與SiC MOSFET器件進(jìn)行比較,在UnitedSiC上進(jìn)行的測試表明,在高漏極電流下,當(dāng)峰值電壓調(diào)諧相當(dāng)時(shí),采用緩沖方案的關(guān)斷能量損耗(EOFF)僅為單單采用柵極電阻時(shí)的50%。同時(shí)導(dǎo)通能耗(EON)略高(僅約10%),對于一個(gè)以40 kHz和48 A / 800 V開關(guān)的40mΩ器件來說,一個(gè)周期約275 µJ(或11 W)的緩沖器對其總體上的影響是正面的。這種比較在圖3中以藍(lán)色和黃色的曲線表示。黑色曲線代表了一個(gè)有緩沖器且優(yōu)化了柵極導(dǎo)通和關(guān)斷電阻的40mΩ UnitedSiC SiC FET器件的性能,與測量的SiC MOSFET相比,SiC FET的輸出電容更低,本征速度更快,因此其損耗得到了進(jìn)一步降低。

圖3:比較SiC開關(guān)有無緩沖器時(shí)的總開關(guān)損耗。

緩沖電容器在每個(gè)開關(guān)周期里都充分地充電和放電,但要注意的是,這些存儲的能量并沒有全部消耗在電阻器上。實(shí)際上,大多數(shù)CV2能量是在器件開啟時(shí)消耗的。在引用示例中,在40 kHz,ID為 40 A,VDS為 800 V以及有著一個(gè)220-pF /10-Ω緩沖器的情況下,總功率消耗約為5 W,但電阻僅占0.8W,其余的都在開關(guān)中消耗了。這樣就可以使用額定電壓合適的小尺寸電阻器(即使是表面貼裝型也可以)。

UnitedSiC的器件具有D2pk7L和DFN8×8以及TO247-4L封裝形式,可實(shí)現(xiàn)最佳的熱性能。 TO247-4L封裝的部件與源極之間有開爾文連接,可有效消除源極電感的影響,減少了開關(guān)損耗,并在高漏極di / dt時(shí)生成更干凈的柵極波形。

結(jié)論

器件緩沖似乎是處理開關(guān)過沖、振鈴和損耗的一種“野蠻”解決方案,而這對于諸如IGBT之類較老的技術(shù)來說確實(shí)如此,因?yàn)樗鼈兊?ldquo;尾電流”長,需要大型且有損的緩沖網(wǎng)絡(luò)。但是,寬禁帶器件,尤其是SiC FET,可以將該技術(shù)用為柵極電阻調(diào)諧的優(yōu)良替代方案,以提供較低的總損耗,并且可以采用緊湊、廉價(jià)的元器件來實(shí)現(xiàn)。

(文章來源:ednchina)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進(jìn)行侵刪。