【導(dǎo)讀】本文討論了一種帶有集成微帶過孔不平衡-平衡器,60GHz毫米波CMOS射頻芯片嵌入式偶極子天線的設(shè)計,制造和晶圓上測量。這是為了利用集成低成本單 片集成CMOS射頻前端電路的天線為60GHz無線電實現(xiàn)一種射頻芯片嵌入式系統(tǒng)(SoC)。

無線網(wǎng)絡(luò)不斷增長的容量,對寬帶多媒體組件的需求不斷增加。特別是對于密集的本地通信來說,指定給無線個人網(wǎng)絡(luò)(WPAN)的60GHz頻帶對于短距通信 具有特殊意義。這是因為在以60GHz為中心頻率的8GHz帶寬內(nèi)由大氣中的氧氣引起的射頻衰減為10到15dB/km。這使60GHz頻段對于所有類型 的短距無線通信具有最重大的意義。為了在60GHz無線電中使用射頻芯片嵌入式系統(tǒng)(SoC)方式,研究了整合低成本單片集成CMOS射頻前端電路的天線。

本文提出了一種60GHz CMOS射頻芯片嵌入式偶極子天線。在這種射頻芯片嵌入式天線的設(shè)計中采用了帶有集成微帶過孔不平衡-平衡器的平面偶極子天線結(jié)構(gòu)。設(shè)計仿真中使用了一種 基于FEM的3-D全波EM solver—Ansoft公司的HFSS。天線芯片使用0.18微米CMOS工藝制造。所設(shè)計的射頻芯片嵌入式天線的輸入VSWR和天線增益晶圓上測量 使用微波探針臺實行。

天線設(shè)計

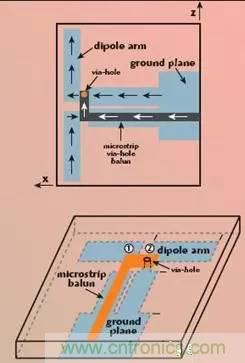

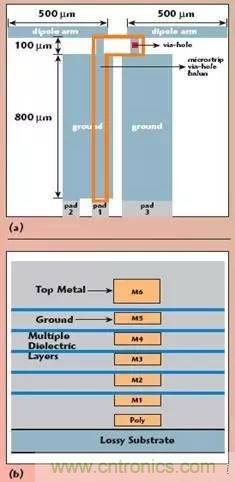

圖1給出了所提的平面印制偶極子天線。微帶過孔不平衡-平衡器用作饋電同軸線和兩個印制偶極子帶之間的不平衡-平衡轉(zhuǎn)換器。偶極子帶的長度約為1/4波 長。微帶線和偶極子帶的接地面在同一個面。就像圖中指出的那樣,過孔允許一個印制偶極子帶的饋電信號(點2)與另一個印制偶極子帶的饋電信號(點1)擁有 相同的相位。因為頂層導(dǎo)體與微帶線的接地面存在180°相差,印制偶極子帶點2的饋電信號會與點1的另一個饋電信號之間存在180°相差。偶極子臂帶寬度 選取為約等于波長的十分之一。微帶饋線寬面的特征阻抗設(shè)計為50 Ω。印制偶極子和集成過孔不平衡-平衡器每個部分的尺寸必須經(jīng)過精確的數(shù)值計算以獲得所需的印制天線性能。圖2給出了所設(shè)計的60GHz射頻芯片嵌入式偶 極子天線的0.18微米CMOS工藝制成芯片布線與切面圖。

仿真與測試結(jié)論

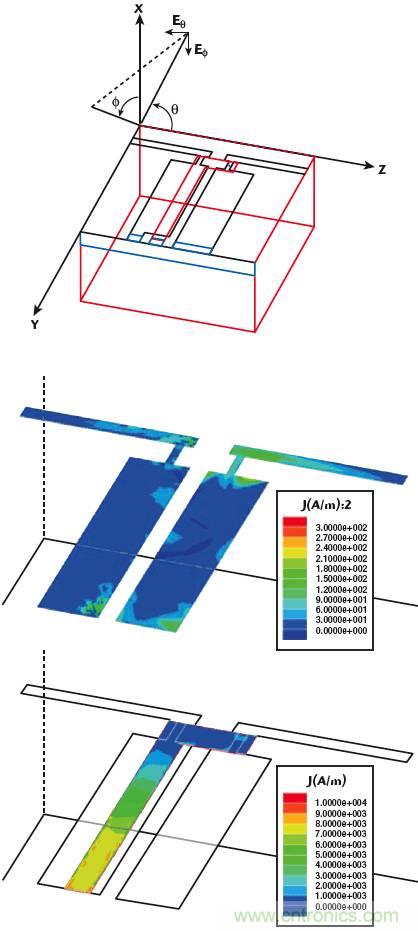

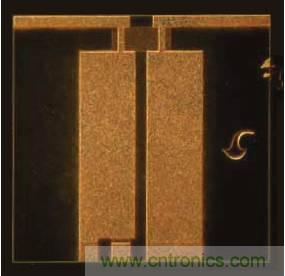

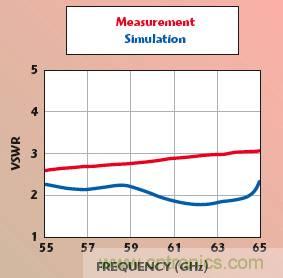

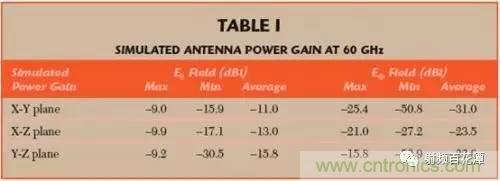

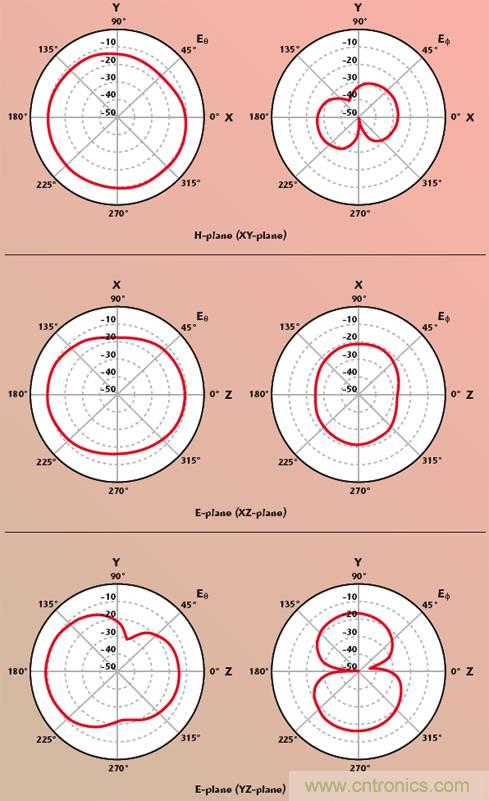

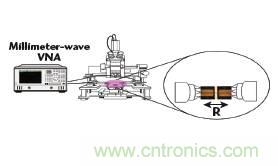

圖3給出了HFSS仿真的天線電流分布。頂面和底面金屬上的仿真電流密度矢量明顯表示出了平衡電流分布和兩個印制偶極子饋電點上電流流動矢量180°相位 差。這展示了集成微帶不平衡-平衡器的作用。圖4給出了一個制成60GHz CMOS射頻芯片嵌入式天線的芯片顯微圖。芯片尺寸為0.75 × 0.66mm,基底厚度約為500mm。圖5給出了天線輸入VSWR晶圓上測量值,其在55到65GHz內(nèi)小于3。圖6和表1給出了60GHz天線仿真輻 射圖樣與H平面、E平面功率增益值。注意到,天線功率增益(絕對增益)Gp定義為:

圖1 帶有集成過孔不平衡-平衡器的平面耦極子天線

圖2 60GHzCMOS射頻芯片嵌入式天線芯片布線(a)和截面圖(b)

圖3 HFSS仿真圖與仿真天線電流分布

圖4 芯片顯微圖

圖5 仿真和實測天線輸入VSWR

表1 60GHz仿真天線功率增益*

圖6 60GHz H平面E平面仿真天線輻射圖樣

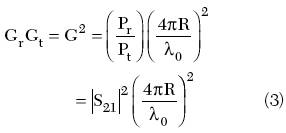

仿真天線輻射效率近似為百分之16。這可能是CMOS基底損耗造成的。H平面圖樣除了在某個特定方向存在一些衰減之外近似為全向圖樣。H平面仿真最大,最 小和平均增益分別近似為-9,-16和-11dBi。用Simons和Lee描述的技術(shù)測得晶圓上測量天線絕對功率增益。如圖7所示,兩個相同的射頻芯片 嵌入式天線面對面距離R放置。其中一個天線為發(fā)射天線,而另一個為接收天線。分隔兩相同天線的距離R應(yīng)滿足遠場條件,即大于等于

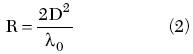

這里D和λ0分別為射頻芯片嵌入式天線最大孔徑與工作頻率自由空間波長。從Friis的功率傳輸公式得知,最大功率天線增益(在偶極子天線的中心前向上)由下式給出:

這里

Gt和Gr =發(fā)送和接收天線增益

Pt =發(fā)送功率

Pr =接收功率

同樣,因為兩天線相同,Gr= Gt=G。功率比Pr/Pt為由VNA得來的實測直接傳輸系數(shù)|S21|2。圖8給出了晶片上測量設(shè)置的探針臺顯微圖。60GHz實測最大天線功率增益約為-10dBi。這與仿真結(jié)論完美一致。表2給出了天線輻射特征的性能總結(jié)。

圖7 射頻芯片嵌入式天線晶片上測試的配置圖示

結(jié)論

本文討論了一種帶有集成微帶過孔不平衡-平衡器,60GHz毫米波CMOS射頻芯片嵌入式偶極子天線的設(shè)計,制造和晶圓上測量。這是為了利用集成低成本單 片集成CMOS射頻前端電路的天線為60GHz無線電實現(xiàn)一種射頻芯片嵌入式系統(tǒng)(SoC)。天線芯片使用0.18微米CMOS工藝制造,芯片尺寸為 0.75 × 0.66 mm。

使用了基于FEM的一種3D全波EM solver—HFSS進行設(shè)計仿真。對輸入VSWR和射頻芯片嵌入式天線的最大天線功率增益做了晶圓上測量。實測天線VSWR在55到65GHz之間小 于3。實測H平面輻射圖樣近似為全向圖樣,而且仿真天線輻射效率近似為16。這可能是CMOS基底損耗引起的。60GHz處實測天線功率增益約為 -10dBi,這與仿真結(jié)果很好地一致。今后將會獲得所設(shè)計的帶有60GHz CMOS射頻前端電路的60GHz射頻芯片嵌入式天線的集成產(chǎn)品。

表2 帶過孔不平衡-平衡器的60GHz CMOS射頻芯片嵌入式偶極子天線性能總結(jié)

圖8 探針臺晶圓測試設(shè)置

(來源:射頻百花潭)

推薦閱讀: