【導(dǎo)讀】大致來說,軟件定義無線電(SDR)是指信號鏈的一部分是軟件的任何無線電。具體來說,它會具有以下部分或全部特性:寬帶、多頻段、多模式、多數(shù)據(jù)速率、軟件可重新配置,并且其數(shù)字轉(zhuǎn)換(接收或傳輸)會盡可能靠近天線。請注意,該描述也適用于現(xiàn)代信號(頻譜)分析儀等RF儀器儀表。

一般認(rèn)為是德克薩斯州加蘭的E-Systems(現(xiàn)Raytheon)公司在1984年構(gòu)建了第一臺軟件定義的基帶接收器,而第一臺軟件定義的基帶收發(fā)器可能是WSC-3(v)9,由E Systems加利福尼亞州佛羅里達(dá)圣彼得堡分部在1987年為Patrick AFB設(shè)計的。1989年,Haseltine和Motorola c.又為Rome AFB開發(fā)出了更新的無線電產(chǎn)品Speakeasy。現(xiàn)代的示例包括衛(wèi)星和地面無線電、軍事聯(lián)合戰(zhàn)術(shù)無線電系統(tǒng)(JTRS)以及幾乎任何蜂窩或陸地移動無線電終端或基站。

從理論上來說,要使數(shù)字轉(zhuǎn)換和信號處理正常工作,我們應(yīng)該具有線性時不變系統(tǒng),但實踐告訴我們,將一系列模擬器件連在一起后就沒有這么理想了。不過,通過精心挑選元件和分布增益,你可以在保持靈敏度的同時最大程度地擴大SDR的動態(tài)范圍。而且,無論SDR是通信接收器基站還是信號分析儀,都適用相同的規(guī)則。

在一些標(biāo)準(zhǔn)通信系統(tǒng)(例如,蜂窩系統(tǒng))中,SDR在受控環(huán)境中工作,也就是說,標(biāo)準(zhǔn)闡明了針對接收器和發(fā)射器的要求,而載波則為標(biāo)準(zhǔn)增加了裕量。在其他一些系統(tǒng)(如軍事、業(yè)余和陸地移動無線電)中,環(huán)境不受控制,也就是說,最近的發(fā)射極可能就在隔壁,最遠(yuǎn)的可能剛好在視距的耳語范圍內(nèi)。

因此,在開始設(shè)計之前,你需要先制定一份檢查清單:

1.標(biāo)準(zhǔn)有哪些要求?

2.所需的最小和最大信號電平是多少?

3.需要多少濾波?

4.哪些圖像濾波器、通道濾波器和抗混疊濾波器可用?

5.濾波器中的群延遲是否會產(chǎn)生問題?

6.您使用的是什么架構(gòu)?零中頻、單通道、雙通道或三通道轉(zhuǎn)換

7.您目前如何生成正交信號?

8.在模擬還是數(shù)字(IF采樣)域中?

選擇ADC本身就值得討論。ADC的動態(tài)范圍可確定系統(tǒng)架構(gòu)(反之亦然)。首先,我們要查看信號帶寬和采樣頻率(準(zhǔn)確的采用頻率通常由時鐘和/ 或幀速率等數(shù)字信號處理要求確定)。為了獲得ADC的滿量程SNR,尤其是對高輸入頻率采樣時,能否生成足夠良好的時鐘,從而在不降低ADC的指定SNR的情況下以所需的頻率采樣?要使系統(tǒng)成為線性時不變系統(tǒng),ADC必須提供足以支持所需信號、干擾信號以及增加的裕量的動態(tài)范圍,以支持信號衰落和AGC響 應(yīng)時間。

那么,多大的動態(tài)范圍才夠呢?性能最高的軟件定義無線電(和RF實驗室儀器)通常采用14至16位高速ADC,從而以盡可能高的頻率對帶寬高達(dá) 250 MHz的信號采樣。為了按照標(biāo)準(zhǔn)(如802.11等字母數(shù)字組合)測試頻帶最寬的信號,行業(yè)偏向于使用14b AD9680等雙通道高速ADC在I和Q帶寬等于或高于500 MHz的基帶中對I和Q信號進(jìn)行正交采樣。一些應(yīng)用程序需要更小的動態(tài)范圍,因此通常使用12b的GSPS ADC(如AD9625)來“抓取”帶寬為500 MHz的頻譜塊,并使用集成數(shù)字下變頻器來調(diào)低其基帶頻率。

ADC的動態(tài)范圍是模擬和數(shù)字濾波之間的基本權(quán)衡。更多的模擬濾波會縮小干擾信號的幅度以及ADC的所需范圍,這就必須對所需的信號和干擾信號 進(jìn)行數(shù)字轉(zhuǎn)換以保持線性系統(tǒng)。但是,模擬濾波并不是理想的方式,它可能會出現(xiàn)群延遲和相位。在系統(tǒng)級別,模擬域的大量濾波操作也意味著可能要進(jìn)行大量費用高昂的機械屏蔽工作以保持濾波器隔離,并且可能需要在多個IF級聯(lián)多個濾波器以最大程度地減少濾波器周圍漏電的情況。相反,數(shù)字濾波器具有出色的形狀因子,沒有漏電,其特性近乎理想,但需要提高ADC的動態(tài)范圍以支持信號和干擾信號。

孰優(yōu)孰劣似乎顯而易見,但你必須將接收器設(shè)計為可在所有工作條件下保持對ADC的線性輸入。例如,這需要你將AGC的響應(yīng)時間結(jié)合到ADC的裕量中,也就是說,允許特定數(shù)量的dB作為裕量以考慮AGC反應(yīng)期間的輸入信號變化,這樣接收器不會因信號電平變化而出現(xiàn)過載。

此外,在UHF和微波信號中,你可能還希望針對信號衰落增加額外裕量,不管這種信號衰落是由于頻率較低還是信號被大樓或植物阻擋等環(huán)境條件而導(dǎo)致的。除此之外,你還需要考慮解調(diào)C/N比、鄰道和相間通道干擾信號以及全雙工系統(tǒng)中可能出現(xiàn)的PA饋通效應(yīng)的裕量。

另外需要記住的是,窄帶接收器的AGC范圍比寬帶接收器更寬?;旧希瑢拵Ы邮掌鲿⒋笃l譜小幅度地上移或下移,通常小于10 dB以使其保持在ADC的線性“窗口”中間。這與對整個蜂窩頻段進(jìn)行數(shù)字轉(zhuǎn)換時一樣。相反,窄帶接收器則高度依賴濾波以最大程度地減少通帶中的信號數(shù),但必須能支持更大的干擾信號。它們通常在不受控的環(huán)境中使用,其AGC可作用于更窄的通帶中的信號。

圖1. ADISIMRF建模工具屏幕截圖(顯示直接變頻接收機)

在為接收器設(shè)計設(shè)置級聯(lián)噪聲系數(shù)和截距模型時,你實際上需要為系統(tǒng)建模三次:一次針對最小信號電平,即最大增益下的AGC關(guān)閉電平;第二次針對最大信號電平,即最大增益衰減下的AGC開啟電平;最后一次針對接收器的標(biāo)稱輸入電平。你還需要在所有三種模型中考慮交調(diào)效應(yīng)。幸運的是,ADI的 ADISIMRF(圖1)等免費工具將助您一臂之力;這類工具通常內(nèi)置適用于RF增益塊、混頻器、衰減器、巴倫、濾波器和高速轉(zhuǎn)換器的模型庫。

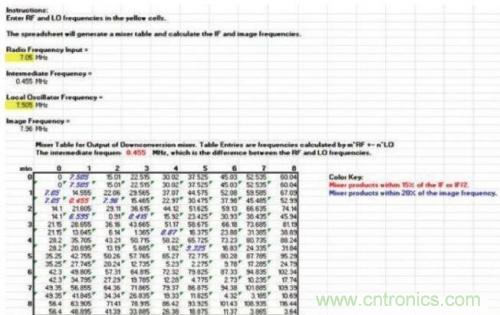

頻率規(guī)劃是另一項需要廣泛研究的有趣課題。你不僅需要為每個混頻器(圖2)制作一個混頻器表,而且可能還希望為發(fā)射路徑制作一個類似的DAC表。此外,你還需要考慮在哪個奈奎斯特頻率區(qū)域使用轉(zhuǎn)換器(ADC或DAC)。系統(tǒng)時鐘通常是幀速率的倍數(shù)(這就是1.2288 MHz和13 MHz的倍數(shù)之所以常見的原因)。幸運的是,你可以使用足夠高的頻率(諧波不在頻帶范圍內(nèi)或目標(biāo)信號上)。你需要通過精心挑選系統(tǒng)時鐘、中頻和本振(LO)頻率來最大程度地減少內(nèi)外部干擾,因為這些頻率將得到無法預(yù)見的混頻產(chǎn)物。

圖2. 樣本混頻器表,顯示在混頻過程中產(chǎn)生的多種nf1 ± mf2產(chǎn)物,其中f1和f2分別是混頻器的RF輸入和本振輸入頻率。

針對級數(shù)和功能類型(濾波器、混頻器、放大器等)設(shè)置了級聯(lián)噪聲系數(shù)和截距模型后,就需要執(zhí)行一些端計算。

例如,你首先需要使用以下等式計算ADC的噪聲系數(shù)(NF)

NF = FS+ 174 dBm – SNR –10 log10 B (at 300°K)

其中PFS是ADC的滿量程輸入功率(以dBm為單位),PFS(dBm) = 10 log10 [PFS (mW)/ 1 mW],SNR是ADC的信噪比(以dB為單位),以及B是要進(jìn)行數(shù)字轉(zhuǎn)換的帶寬,需要考慮輸入濾波器的噪聲帶寬(圖3)。

圖3:巴特沃茲濾波器的噪聲帶寬與3 dB帶寬的關(guān)系。

請注意,如果你希望將所需信號加上干擾信號進(jìn)行數(shù)字轉(zhuǎn)換以濾除數(shù)字域中的干擾信號,此帶寬可能比信號帶寬更寬。幸運的是,你可以通過對輸入信號過采樣來提高ADC的噪聲系數(shù)。在這種情況下,計算噪聲系數(shù)的等式將變?yōu)?/div>

NF = PFS+ 174 dBm – SNR – 10 log10 B – 10 log10 [fs/2B],

其中,fs是采樣時鐘,B仍然是信號帶寬(或要進(jìn)行數(shù)字處理的帶寬)。一些IF采樣ADC(如AD9874和AD9864)會在帶通-架構(gòu)中使用過采樣和噪聲整形。這些ADC實際上是完整的IF子系統(tǒng) – 接受IF輸入并提供接近100 dB的SNR,以及在輸出時抽取的16或24位I和Q數(shù)據(jù)。

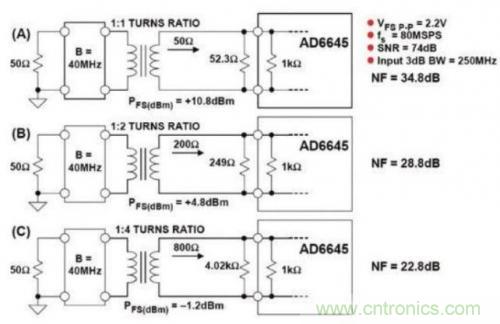

過采樣并不是改善ADC噪聲系數(shù)的唯一途徑。您你可以使用變壓器在“無噪聲”增益下提高ADC的輸入電壓。

表1. 應(yīng)用“無噪聲”電壓增益可以提高性能,但不會使ADC過驅(qū)。

你需要完成的最后一個端計算是針對轉(zhuǎn)換時鐘的。具有(或缺乏)生成低抖動時鐘的能力是針對高動態(tài)范圍的接收器未在天線中放置ADC的原因所在, 我們將在下面對此進(jìn)行介紹。計算ADC理論上的SNR(作為時鐘抖動的函數(shù))的等式為SNR = 20 log10[1/(2ftj)],其中f是正在采樣的頻率(以Hz為單位)以及tj是時鐘抖動(以秒為單位)?;蛘撸o定所需的SNR(以dB為單位)和最大輸入頻率f (以Hz為單位),tj= 1/(2f10[SNR/20])。

例如,在進(jìn)行IF采樣時,如果你希望在IF為240 MHz時對20 MHz寬的信號采樣,則頻率最高的采樣元件將是IF加上信號帶寬的一半(或250 MHz)。SNR為80 dB,最大輸入頻率為250 MHz時,可通過求解得出最大時鐘抖動為63.66 fs。你可以仿真PLL/VCO的性能,并使用ADISIMPLL和ADISIMCLK等免費工具計算各類環(huán)路濾波器以及電路配置的抖動。借助這些工具,你可以優(yōu)化環(huán)路濾波器的設(shè)計以獲得最佳相位噪聲,進(jìn)而最大程度地減少抖動,這種做法的代價是會增加濾波器的建立時間,但這對高速ADC的固定頻率時鐘來說 通常不是問題。

到目前為止,我們已經(jīng)回顧了一些旨在最大程度地擴大軟件定義無線電的動態(tài)范圍的電路元件、計算和仿真工具,并重點關(guān)注ADC的性能和頻率規(guī)劃。由于篇幅限制,我們略去了增益和增益分布對失真的影響這一主題,但可在日后再對其進(jìn)行介紹。