【導(dǎo)讀】芯片制造的過程就如同用樂高蓋房子一樣,先有晶圓作為地基,再層層往上疊的芯片制造流程后,就可產(chǎn)出必要的 IC 芯片(這些會在后面介紹)。然而,沒有設(shè)計(jì)圖,擁有再強(qiáng)制造能力都沒有用,因此,建筑師的角色相當(dāng)重要。但是 IC 設(shè)計(jì)中的建筑師究竟是誰呢?本文接下來要針對 IC設(shè)計(jì)、制造到封裝的全流程做介紹。

一、復(fù)雜繁瑣的芯片設(shè)計(jì)流程

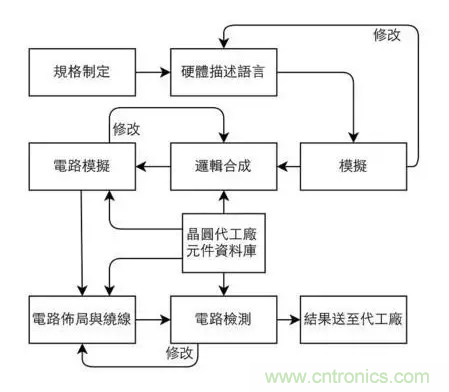

在 IC 生產(chǎn)流程中,IC 多由專業(yè) IC 設(shè)計(jì)公司進(jìn)行規(guī)劃、設(shè)計(jì),像是聯(lián)發(fā)科、高通、Intel 等知名大廠,都自行設(shè)計(jì)各自的 IC 芯片,提供不同規(guī)格、效能的芯片給下游廠商選擇。因?yàn)?IC 是由各廠自行設(shè)計(jì),所以 IC 設(shè)計(jì)十分仰賴工程師的技術(shù),工程師的素質(zhì)影響著一間企業(yè)的價值。然而,工程師們在設(shè)計(jì)一顆 IC 芯片時,究竟有那些步驟?設(shè)計(jì)流程可以簡單分成如下。

設(shè)計(jì)第一步,訂定目標(biāo)

在 IC 設(shè)計(jì)中,最重要的步驟就是規(guī)格制定。這個步驟就像是在設(shè)計(jì)建筑前,先決定要幾間房間、浴室,有什么建筑法規(guī)需要遵守,在確定好所有的功能之后在進(jìn)行設(shè)計(jì), 這樣才不用再花額外的時間進(jìn)行后續(xù)修改。IC 設(shè)計(jì)也需要經(jīng)過類似的步驟,才能確保設(shè)計(jì)出來的芯片不會有任何差錯。

規(guī)格制定的第一步便是確定 IC 的目的、效能為何,對大方向做設(shè)定。接著是察看有哪些協(xié)定要符合,像無線網(wǎng)卡的芯片就需要符合 IEEE 802.11 等規(guī)範(fàn),不然,這芯片將無法和市面上的產(chǎn)品相容,使它無法和其他設(shè)備連線。最后則是確立這顆 IC 的實(shí)作方法,將不同功能分配成不同的單元,并確立不同單元間連結(jié)的方法,如此便完成規(guī)格的制定。

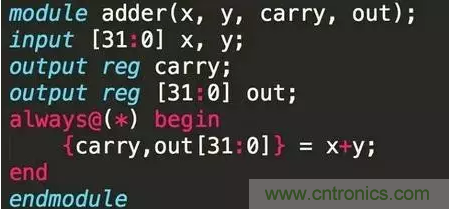

設(shè)計(jì)完規(guī)格后,接著就是設(shè)計(jì)芯片的細(xì)節(jié)了。這個步驟就像初步記下建筑的規(guī)畫,將整體輪廓描繪出來,方便后續(xù)制圖。在 IC 芯片中,便是使用硬體描述語言(HDL)將電路描寫出來。常使用的 HDL 有 Verilog、VHDL 等,藉由程式碼便可輕易地將一顆 IC 地功能表達(dá)出來。接著就是檢查程式功能的正確性并持續(xù)修改,直到它滿足期望的功能為止。

▲ 32 bits 加法器的 Verilog 范例

有了電腦,事情都變得容易

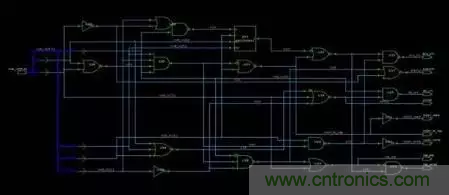

有了完整規(guī)畫后,接下來便是畫出平面的設(shè)計(jì)藍(lán)圖。在 IC 設(shè)計(jì)中,邏輯合成這個步驟便是將確定無誤的 HDL code,放入電子設(shè)計(jì)自動化工具(EDA tool),讓電腦將 HDL code 轉(zhuǎn)換成邏輯電路,產(chǎn)生如下的電路圖。之后,反覆的確定此邏輯閘設(shè)計(jì)圖是否符合規(guī)格并修改,直到功能正確為止。

▲ 控制單元合成后的結(jié)果

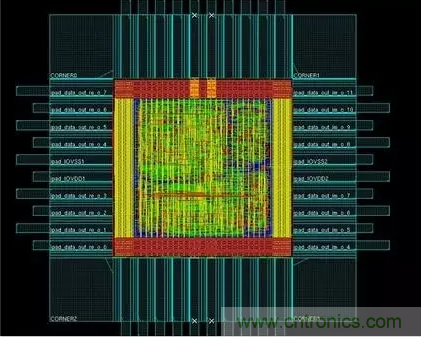

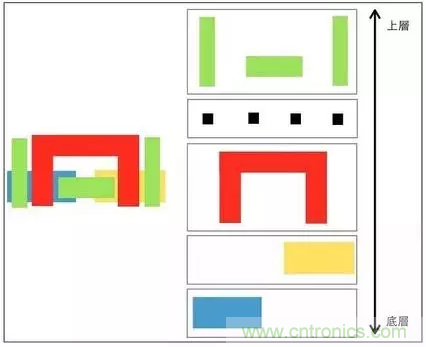

最后,將合成完的程式碼再放入另一套 EDA tool,進(jìn)行電路布局與繞線(Place And Route)。在經(jīng)過不斷的檢測后,便會形成如下的電路圖。圖中可以看到藍(lán)、紅、綠、黃等不同顏色,每種不同的顏色就代表著一張光罩。至于光罩究竟要如何運(yùn)用呢?

▲ 常用的演算芯片- FFT 芯片,完成電路布局與繞線的結(jié)果

層層光罩,疊起一顆芯片

首先,目前已經(jīng)知道一顆 IC 會產(chǎn)生多張的光罩,這些光罩有上下層的分別,每層有各自的任務(wù)。下圖為簡單的光罩例子,以積體電路中最基本的元件 CMOS 為範(fàn)例,CMOS 全名為互補(bǔ)式金屬氧化物半導(dǎo)體(Complementary metal–oxide–semiconductor),也就是將 NMOS 和 PMOS 兩者做結(jié)合,形成 CMOS。至于什么是金屬氧化物半導(dǎo)體(MOS)?這種在芯片中廣泛使用的元件比較難說明,一般讀者也較難弄清,在這裡就不多加細(xì)究。

下圖中,左邊就是經(jīng)過電路布局與繞線后形成的電路圖,在前面已經(jīng)知道每種顏色便代表一張光罩。右邊則是將每張光罩?jǐn)傞_的樣子。制作是,便由底層開始,依循上一篇 IC 芯片的制造中所提的方法,逐層制作,最后便會產(chǎn)生期望的芯片了。

至此,對于 IC 設(shè)計(jì)應(yīng)該有初步的了解,整體看來就很清楚 IC 設(shè)計(jì)是一門非常復(fù)雜的專業(yè),也多虧了電腦輔助軟體的成熟,讓 IC 設(shè)計(jì)得以加速。IC 設(shè)計(jì)廠十分依賴工程師的智慧,這裡所述的每個步驟都有其專門的知識,皆可獨(dú)立成多門專業(yè)的課程,像是撰寫硬體描述語言就不單純的只需要熟悉程式語言,還需 要了解邏輯電路是如何運(yùn)作、如何將所需的演算法轉(zhuǎn)換成程式、合成軟體是如何將程式轉(zhuǎn)換成邏輯閘等問題。

二、什么是晶圓?

在半導(dǎo)體的新聞中,總是會提到以尺寸標(biāo)示的晶圓廠,如 8 寸或是 12 寸晶圓廠,然而,所謂的晶圓到底是什么東西?其中 8 寸指的是什么部分?要產(chǎn)出大尺寸的晶圓制造又有什么難度呢?以下將逐步介紹半導(dǎo)體最重要的基礎(chǔ)——「晶圓」到底是什么。

晶圓(wafer),是制造各式電腦芯片的基礎(chǔ)。我們可以將芯片制造比擬成用樂高積木蓋房子,藉由一層又一層的堆疊,完成自己期望的造型(也就是各式芯 片)。然而,如果沒有良好的地基,蓋出來的房子就會歪來歪去,不合自己所意,為了做出完美的房子,便需要一個平穩(wěn)的基板。對芯片制造來說,這個基板就是接 下來將描述的晶圓。

(Souse:Flickr/Jonathan Stewart CC BY 2.0)

首先,先回想一下小時候在玩樂高積木時,積木的表面都會有一個一個小小圓型的凸出物,藉由這個構(gòu)造,我們可將兩塊積木穩(wěn)固的疊在一起,且不需使用膠水。芯片制造,也是以類似這樣的方式,將后續(xù)添加的原子和基板固定在一起。因此,我們需要尋找表面整齊的基板,以滿足后續(xù)制造所需的條件。

在固體材料中,有一種特殊的晶體結(jié)構(gòu)──單晶(Monocrystalline)。它具有原子一個接著一個緊密排列在一起的特性,可以形成一個平整的原 子表層。因此,采用單晶做成晶圓,便可以滿足以上的需求。然而,該如何產(chǎn)生這樣的材料呢,主要有二個步驟,分別為純化以及拉晶,之后便能完成這樣的材料。

如何制造單晶的晶圓

純化分成兩個階段,第一步是冶金級純化,此一過程主要是加入碳,以氧化還原的方式,將氧化硅轉(zhuǎn)換成 98% 以上純度的硅。大部份的金屬提煉,像是鐵或銅等金屬,皆是采用這樣的方式獲得足夠純度的金屬。但是,98% 對于芯片制造來說依舊不夠,仍需要進(jìn)一步提升。因此,將再進(jìn)一步采用西門子制程(Siemens process)作純化,如此,將獲得半導(dǎo)體制程所需的高純度多晶硅。

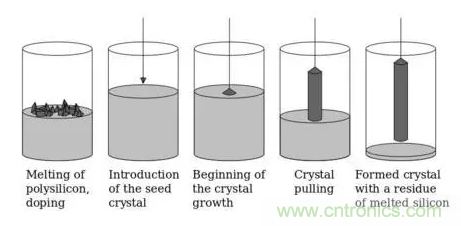

▲ 硅柱制造流程(Source:Wikipedia)

接著,就是拉晶的步驟。首先,將前面所獲得的高純度多晶硅融化,形成液態(tài)的硅。之后,以單晶的硅種(seed)和液體表面接觸,一邊旋轉(zhuǎn)一邊緩慢的向上 拉起。至于為何需要單晶的硅種,是因?yàn)楣柙优帕芯秃腿伺抨?duì)一樣,會需要排頭讓后來的人該如何正確的排列,硅種便是重要的排頭,讓后來的原子知道該如何排 隊(duì)。最后,待離開液面的硅原子凝固后,排列整齊的單晶硅柱便完成了。

▲ 單晶硅柱(Souse:Wikipedia)

然而,8寸、12寸又代表什么東西呢?他指的是我們產(chǎn)生的晶柱,長得像鉛筆筆桿的部分,表面經(jīng)過處理并切成薄圓片后的直徑。至于制造大尺寸晶圓又有什么 難度呢?如前面所說,晶柱的制作過程就像是在做棉花糖一樣,一邊旋轉(zhuǎn)一邊成型。有制作過棉花糖的話,應(yīng)該都知道要做出大而且扎實(shí)的棉花糖是相當(dāng)困難的,而 拉晶的過程也是一樣,旋轉(zhuǎn)拉起的速度以及溫度的控制都會影響到晶柱的品質(zhì)。也因此,尺寸愈大時,拉晶對速度與溫度的要求就更高,因此要做出高品質(zhì) 12 寸晶圓的難度就比 8 寸晶圓還來得高。

只是,一整條的硅柱并無法做成芯片制造的基板,為了產(chǎn)生一片一片的硅晶圓,接著需要以鉆石刀將硅晶柱橫向切成圓片,圓片再經(jīng)由拋光便可形成芯片制造所需的 硅晶圓。經(jīng)過這么多步驟,芯片基板的制造便大功告成,下一步便是堆疊房子的步驟,也就是芯片制造。至于該如何制作芯片呢?

層層堆疊打造的芯片

在介紹過硅晶圓是什么東西后,同時,也知道制造 IC 芯片就像是用樂高積木蓋房子一樣,藉由一層又一層的堆疊,創(chuàng)造自己所期望的造型。然而,蓋房子有相當(dāng)多的步驟,IC 制造也是一樣,制造 IC 究竟有哪些步驟?本文將將就 IC 芯片制造的流程做介紹。

在開始前,我們要先認(rèn)識 IC 芯片是什么。IC,全名積體電路(Integrated Circuit),由它的命名可知它是將設(shè)計(jì)好的電路,以堆疊的方式組合起來。藉由這個方法,我們可以減少連接電路時所需耗費(fèi)的面積。下圖為 IC 電路的 3D 圖,從圖中可以看出它的結(jié)構(gòu)就像房子的樑和柱,一層一層堆疊,這也就是為何會將 IC 制造比擬成蓋房子。

▲ IC 芯片的 3D 剖面圖。(Source:Wikipedia)

從上圖中 IC 芯片的 3D 剖面圖來看,底部深藍(lán)色的部分就是上一篇介紹的晶圓,從這張圖可以更明確的知道,晶圓基板在芯片中扮演的角色是何等重要。至于紅色以及土黃色的部分,則是于 IC 制作時要完成的地方。

首先,在這裡可以將紅色的部分比擬成高樓中的一樓大廳。一樓大廳,是一棟房子的門戶,出入都由這裡,在掌握交通下通常會有較多的機(jī)能性。因此,和其他樓 層相比,在興建時會比較復(fù)雜,需要較多的步驟。在 IC 電路中,這個大廳就是邏輯閘層,它是整顆 IC 中最重要的部分,藉由將多種邏輯閘組合在一起,完成功能齊全的 IC 芯片。

黃色的部分,則像是一般的樓層。和一樓相比,不會有太復(fù)雜的構(gòu)造,而且每層樓在興建時也不會有太多變化。這一層的目的,是將紅色部分的邏輯閘相連在一 起。之所以需要這么多層,是因?yàn)橛刑嗑€路要連結(jié)在一起,在單層無法容納所有的線路下,就要多疊幾層來達(dá)成這個目標(biāo)了。在這之中,不同層的線路會上下相連 以滿足接線的需求。

分層施工,逐層架構(gòu)

知道 IC 的構(gòu)造后,接下來要介紹該如何制作。試想一下,如果要以油漆噴罐做精細(xì)作圖時,我們需先割出圖形的遮蓋板,蓋在紙上。接著再將油漆均勻地噴在紙上,待油 漆乾后,再將遮板拿開。不斷的重復(fù)這個步驟后,便可完成整齊且復(fù)雜的圖形。制造 IC 就是以類似的方式,藉由遮蓋的方式一層一層的堆疊起來。

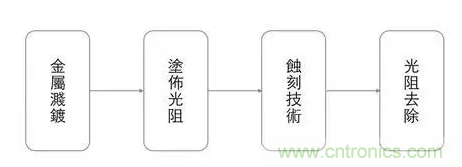

制作 IC 時,可以簡單分成以上 4 種步驟。雖然實(shí)際制造時,制造的步驟會有差異,使用的材料也有所不同,但是大體上皆采用類似的原理。這個流程和油漆作畫有些許不同,IC 制造是先涂料再加做遮蓋,油漆作畫則是先遮蓋再作畫。以下將介紹各流程。

金屬濺鍍:將欲使用的金屬材料均勻?yàn)⒃诰A片上,形成一薄膜。

涂布光阻:先將光阻材料放在晶圓片上,透過光罩(光罩原理留待下次說明),將光束打在不要的部分上,破壞光阻材料結(jié)構(gòu)。接著,再以化學(xué)藥劑將被破壞的材料洗去。

蝕刻技術(shù):將沒有受光阻保護(hù)的硅晶圓,以離子束蝕刻。

光阻去除:使用去光阻液皆剩下的光阻溶解掉,如此便完成一次流程。

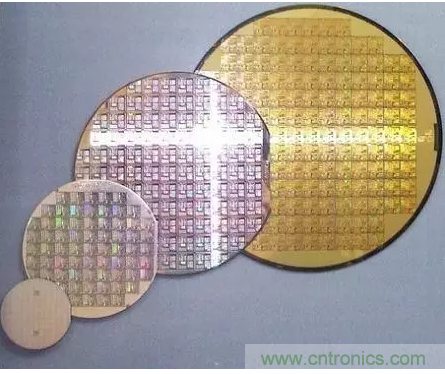

最后便會在一整片晶圓上完成很多 IC 芯片,接下來只要將完成的方形 IC 芯片剪下,便可送到封裝廠做封裝,至于封裝廠是什么東西?就要待之后再做說明啰。

▲ 各種尺寸晶圓的比較。(Source:Wikipedia)

三、納米制程是什么?

三星以及臺積電在先進(jìn)半導(dǎo)體制程打得相當(dāng)火熱,彼此都想要在晶圓代工中搶得先機(jī)以爭取訂單,幾乎成了 14 納米與 16 納米之爭,然而 14 納米與 16 納米這兩個數(shù)字的究竟意義為何,指的又是哪個部位?而在縮小制程后又將來帶來什么好處與難題?以下我們將就納米制程做簡單的說明。

納米到底有多細(xì)微?

在開始之前,要先了解納米究竟是什么意思。在數(shù)學(xué)上,納米是 0.000000001 公尺,但這是個相當(dāng)差的例子,畢竟我們只看得到小數(shù)點(diǎn)后有很多個零,卻沒有實(shí)際的感覺。如果以指甲厚度做比較的話,或許會比較明顯。

用尺規(guī)實(shí)際測量的話可以得知指甲的厚度約為 0.0001 公尺(0.1 毫米),也就是說試著把一片指甲的側(cè)面切成 10 萬條線,每條線就約等同于 1 納米,由此可略為想像得到 1 納米是何等的微小了。

知道納米有多小之后,還要理解縮小制程的用意,縮小電晶體的最主要目的,就是可以在更小的芯片中塞入更多的電晶體,讓芯片不會因技術(shù)提升而變得更大;其 次,可以增加處理器的運(yùn)算效率;再者,減少體積也可以降低耗電量;最后,芯片體積縮小后,更容易塞入行動裝置中,滿足未來輕薄化的需求。

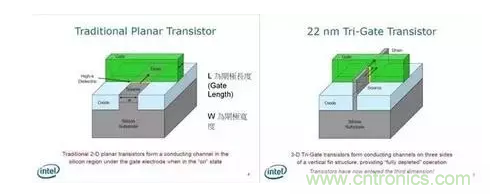

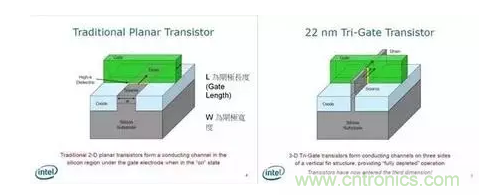

再回來探究納米制程是什么,以 14 納米為例,其制程是指在芯片中,線最小可以做到 14 納米的尺寸,下圖為傳統(tǒng)電晶體的長相,以此作為例子??s小電晶體的最主要目的就是為了要減少耗電量,然而要縮小哪個部分才能達(dá)到這個目的?左下圖中的 L 就是我們期望縮小的部分。藉由縮小閘極長度,電流可以用更短的路徑從 Drain 端到 Source 端(有興趣的話可以利用 Google 以 MOSFET 搜尋,會有更詳細(xì)的解釋)。

此外,電腦是以 0 和 1 作運(yùn)算,要如何以電晶體滿足這個目的呢?做法就是判斷電晶體是否有電流流通。當(dāng)在 Gate 端(綠色的方塊)做電壓供給,電流就會從 Drain 端到 Source 端,如果沒有供給電壓,電流就不會流動,這樣就可以表示 1 和 0。(至于為什么要用 0 和 1 作判斷,有興趣的話可以去查布林代數(shù),我們是使用這個方法作成電腦的)

尺寸縮小有其物理限制

不過,制程并不能無限制的縮小,當(dāng)我們將電晶體縮小到 20 納米左右時,就會遇到量子物理中的問題,讓電晶體有漏電的現(xiàn)象,抵銷縮小 L 時獲得的效益。作為改善方式,就是導(dǎo)入 FinFET(Tri-Gate)這個概念,如右上圖。在 Intel 以前所做的解釋中,可以知道藉由導(dǎo)入這個技術(shù),能減少因物理現(xiàn)象所導(dǎo)致的漏電現(xiàn)象。

更重要的是,藉由這個方法可以增加 Gate 端和下層的接觸面積。在傳統(tǒng)的做法中(左上圖),接觸面只有一個平面,但是采用 FinFET(Tri-Gate)這個技術(shù)后,接觸面將變成立體,可以輕易的增加接觸面積,這樣就可以在保持一樣的接觸面積下讓 Source-Drain 端變得更小,對縮小尺寸有相當(dāng)大的幫助。

最后,則是為什么會有人說各大廠進(jìn)入 10 納米制程將面臨相當(dāng)嚴(yán)峻的挑戰(zhàn),主因是 1 顆原子的大小大約為 0.1 納米,在 10 納米的情況下,一條線只有不到 100 顆原子,在制作上相當(dāng)困難,而且只要有一個原子的缺陷,像是在制作過程中有原子掉出或是有雜質(zhì),就會產(chǎn)生不知名的現(xiàn)象,影響產(chǎn)品的良率。

如果無法想像這個難度,可以做個小實(shí)驗(yàn)。在桌上用 100 個小珠子排成一個 10×10 的正方形,并且剪裁一張紙蓋在珠子上,接著用小刷子把旁邊的的珠子刷掉,最后使他形成一個 10×5 的長方形。這樣就可以知道各大廠所面臨到的困境,以及達(dá)成這個目標(biāo)究竟是多么艱巨。

隨著三星以及臺積電在近期將完成 14 納米、16 納米 FinFET 的量產(chǎn),兩者都想爭奪 Apple 下一代的 iPhone 芯片代工,我們將看到相當(dāng)精彩的商業(yè)競爭,同時也將獲得更加省電、輕薄的手機(jī),要感謝摩爾定律所帶來的好處呢。

四、告訴你什么是封裝

封裝,IC 芯片的最終防護(hù)與統(tǒng)整

經(jīng)過漫長的流程,從設(shè)計(jì)到制造,終于獲得一顆 IC 芯片了。然而一顆芯片相當(dāng)小且薄,如果不在外施加保護(hù),會被輕易的刮傷損壞。此外,因?yàn)樾酒某叽缥⑿?,如果不用一個較大尺寸的外殼,將不易以人工安置在電路板上。因此,本文接下來要針對封裝加以描述介紹。

目前常見的封裝有兩種,一種是電動玩具內(nèi)常見的,黑色長得像蜈蚣的 DIP 封裝,另一為購買盒裝 CPU 時常見的 BGA 封裝。至于其他的封裝法,還有早期 CPU 使用的 PGA(Pin Grid Array;Pin Grid Array)或是 DIP 的改良版 QFP(塑料方形扁平封裝)等。因?yàn)橛刑喾N封裝法,以下將對 DIP 以及 BGA 封裝做介紹。

傳統(tǒng)封裝,歷久不衰

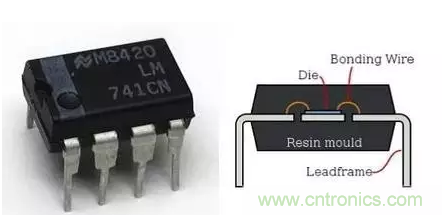

首先要介紹的是雙排直立式封裝(Dual Inline Package;DIP),從下圖可以看到采用此封裝的 IC 芯片在雙排接腳下,看起來會像條黑色蜈蚣,讓人印象深刻,此封裝法為最早采用的 IC 封裝技術(shù),具有成本低廉的優(yōu)勢,適合小型且不需接太多線的芯片。但是,因?yàn)榇蠖嗖捎玫氖撬芰希嵝Ч^差,無法滿足現(xiàn)行高速芯片的要求。因此,使用此 封裝的,大多是歷久不衰的芯片,如下圖中的 OP741,或是對運(yùn)作速度沒那么要求且芯片較小、接孔較少的 IC 芯片。

▲ 左圖的 IC 芯片為 OP741,是常見的電壓放大器。右圖為它的剖面圖,這個封裝是以金線將芯片接到金屬接腳(Leadframe)。(Source :左圖 Wikipedia、右圖 Wikipedia)

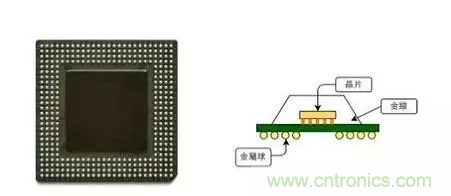

至于球格陣列(Ball Grid Array,BGA)封裝,和 DIP 相比封裝體積較小,可輕易的放入體積較小的裝置中。此外,因?yàn)榻幽_位在芯片下方,和 DIP 相比,可容納更多的金屬接腳相當(dāng)適合需要較多接點(diǎn)的芯片。然而,采用這種封裝法成本較高且連接的方法較復(fù)雜,因此大多用在高單價的產(chǎn)品上。

▲ 左圖為采用 BGA 封裝的芯片。右圖為使用覆晶封裝的 BGA 示意圖。(Source:左圖 Wikipedia)

行動裝置興起,新技術(shù)躍上舞臺

然而,使用以上這些封裝法,會耗費(fèi)掉相當(dāng)大的體積。像現(xiàn)在的行動裝置、穿戴裝置等,需要相當(dāng)多種元件,如果各個元件都獨(dú)立封裝,組合起來將耗費(fèi)非常大的 空間,因此目前有兩種方法,可滿足縮小體積的要求,分別為 SoC(System On Chip)以及 SiP(System In Packet)。

在智慧型手機(jī)剛興 起時,在各大財(cái)經(jīng)雜誌上皆可發(fā)現(xiàn) SoC 這個名詞,然而 SoC 究竟是什么東西?簡單來說,就是將原本不同功能的 IC,整合在一顆芯片中。藉由這個方法,不單可以縮小體積,還可以縮小不同 IC 間的距離,提升芯片的計(jì)算速度。至于制作方法,便是在 IC 設(shè)計(jì)階段時,將各個不同的 IC 放在一起,再透過先前介紹的設(shè)計(jì)流程,制作成一張光罩。

然而,SoC 并非只有優(yōu)點(diǎn),要設(shè)計(jì)一顆 SoC 需要相當(dāng)多的技術(shù)配合。IC 芯片各自封裝時,各有封裝外部保護(hù),且 IC 與 IC 間的距離較遠(yuǎn),比較不會發(fā)生交互干擾的情形。但是,當(dāng)將所有 IC 都包裝在一起時,就是噩夢的開始。IC 設(shè)計(jì)廠要從原先的單純設(shè)計(jì) IC,變成了解并整合各個功能的 IC,增加工程師的工作量。此外,也會遇到很多的狀況,像是通訊芯片的高頻訊號可能會影響其他功能的 IC 等情形。

此外,SoC 還需要獲得其他廠商的 IP(intellectual property)授權(quán),才能將別人設(shè)計(jì)好的元件放到 SoC 中。因?yàn)橹谱?SoC 需要獲得整顆 IC 的設(shè)計(jì)細(xì)節(jié),才能做成完整的光罩,這同時也增加了 SoC 的設(shè)計(jì)成本。或許會有人質(zhì)疑何不自己設(shè)計(jì)一顆就好了呢?因?yàn)樵O(shè)計(jì)各種 IC 需要大量和該 IC 相關(guān)的知識,只有像 Apple 這樣多金的企業(yè),才有預(yù)算能從各知名企業(yè)挖角頂尖工程師,以設(shè)計(jì)一顆全新的 IC,透過合作授權(quán)還是比自行研發(fā)劃算多了。

折衷方案,SiP 現(xiàn)身

作為替代方案,SiP 躍上整合芯片的舞臺。和 SoC 不同,它是購買各家的 IC,在最后一次封裝這些 IC,如此便少了 IP 授權(quán)這一步,大幅減少設(shè)計(jì)成本。此外,因?yàn)樗鼈兪歉髯元?dú)立的 IC,彼此的干擾程度大幅下降。

▲ Apple Watch 采用 SiP 技術(shù)將整個電腦架構(gòu)封裝成一顆芯片,不單滿足期望的效能還縮小體積,讓手錶有更多的空間放電池。(Source:Apple 官網(wǎng))

采用 SiP 技術(shù)的產(chǎn)品,最著名的非 Apple Watch 莫屬。因?yàn)?Watch 的內(nèi)部空間太小,它無法采用傳統(tǒng)的技術(shù),SoC 的設(shè)計(jì)成本又太高,SiP 成了首要之選。藉由 SiP 技術(shù),不單可縮小體積,還可拉近各個 IC 間的距離,成為可行的折衷方案。下圖便是 Apple Watch 芯片的結(jié)構(gòu)圖,可以看到相當(dāng)多的 IC 包含在其中。

▲ Apple Watch 中采用 SiP 封裝的 S1 芯片內(nèi)部配置圖。(Source:chipworks)

完成封裝后,便要進(jìn)入測試的階段,在這個階段便要確認(rèn)封裝完的 IC 是否有正常的運(yùn)作,正確無誤之后便可出貨給組裝廠,做成我們所見的電子產(chǎn)品。至此,半導(dǎo)體產(chǎn)業(yè)便完成了整個生產(chǎn)的任務(wù)。

來源:手機(jī)技術(shù)資訊