【導讀】頻譜擁堵、更高工作頻率和更復雜的波形,給電子監(jiān)控與對抗系統(tǒng)帶來層出不窮的問題,需要偵測的帶寬越來越大,檢測靈敏度要求也越來越高。隨著越來越多的功能通過數(shù)字域?qū)崿F(xiàn),上述帶寬和靈敏度兩個因素,加上成本,直接把高速模數(shù)轉(zhuǎn)換器(ADC)的性能推向極限,常常使ADC成為系統(tǒng)的局限所在。所幸的是,新一代高速ADC的性能水平符合要求,可提供一些系統(tǒng)級解決方案來應對這些挑戰(zhàn)。

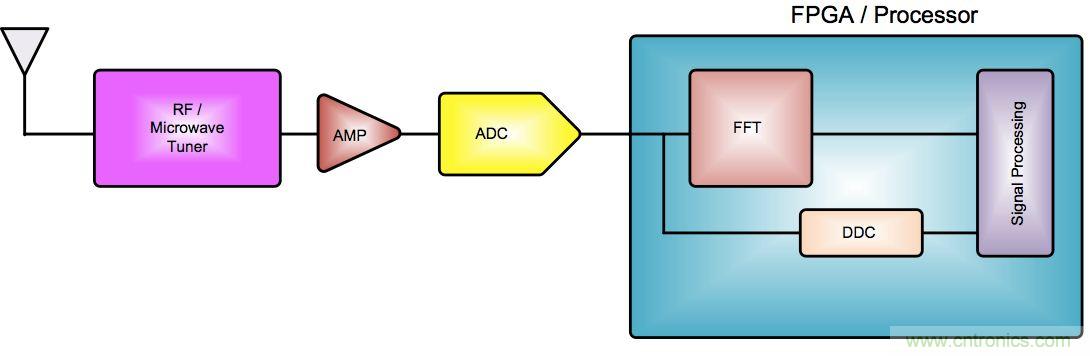

現(xiàn)代監(jiān)控系統(tǒng)的架構如圖1所示,它包括三個基本功能:

● 射頻/微波調(diào)諧器

● 數(shù)字化儀,ADC及相關的放大器和緩沖器

● 快速傅里葉變換和數(shù)字信號處理

很多情況下,高速ADC性能——從模擬域到數(shù)字域的轉(zhuǎn)換——成為系統(tǒng)的限制因素。 盡管最大限度降低成本和系統(tǒng)尺寸始終極其重要,但系統(tǒng)設計人員還必須關注如何最佳地平衡提高瞬時監(jiān)控帶寬的需求(以便最大限度提高攔截概率),以及如何將帶內(nèi)高功率信號降低系統(tǒng)靈敏度的影響減至最少。

表1: 高線性度低速ADC與過去和現(xiàn)在的GSPS ADC的對比

關于如何達到系統(tǒng)指標和已確定的取舍要求,ADC的采樣速率和無雜散動態(tài)范圍(SFDR)通常是影響決策的兩大主要因素。轉(zhuǎn)換器的采樣速率決定奈奎斯特頻段,進而決定個別轉(zhuǎn)換器的最大可觀測帶寬;SFDR決定可檢測的信號電平。雖然噪聲頻譜密度可能也需要考慮,但在多數(shù)情況下,ADC的噪底遠低于雜散水平,而且從系統(tǒng)運行角度看,數(shù)字化過程中產(chǎn)生的雜散與頻譜中進行數(shù)字化的低功率信號難以區(qū)分。因此,系統(tǒng)的靈敏度與SFDR直接相關,這樣檢測到假目標的可能性最低。

例如,考慮對兩個連續(xù)波(CW)信號進行數(shù)字化處理,信號A是一個滿量程輸入,信號B的功率則低得多。作為目標信號的信號B與數(shù)字化信號A所產(chǎn)生的雜散可能難以區(qū)別,因為二者的電平相似。 所以,信號B可能低于系統(tǒng)的檢測電平,不會被標示為目標信號。

圖1: 監(jiān)控系統(tǒng)基本架構

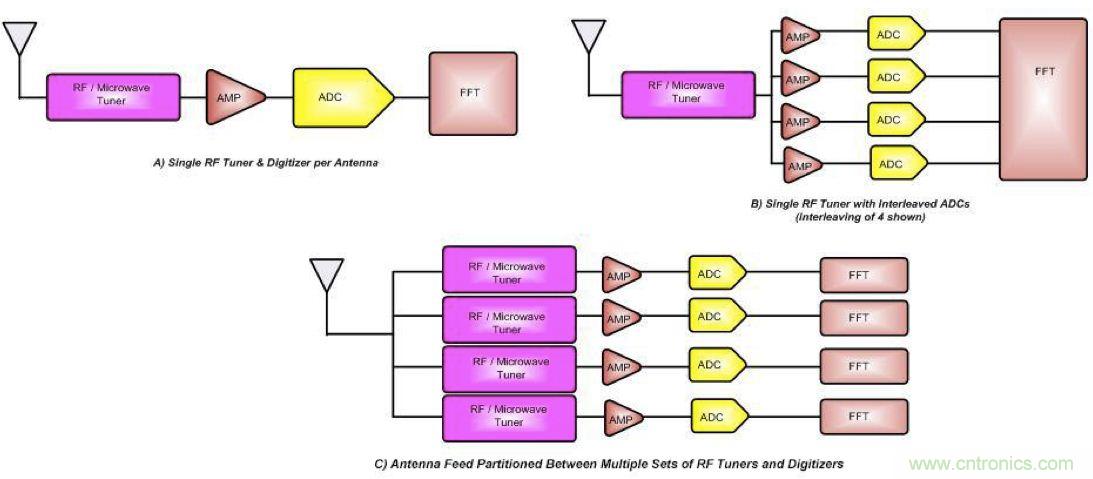

諸如此類的限制表明:利用具有超高線性度的ADC可實現(xiàn)最佳檢測電平,但高線性度傳統(tǒng)上是通過犧牲ADC采樣速率來實現(xiàn)的。為了方便討論,本文考慮一個通用電子監(jiān)控系統(tǒng),但類似的系統(tǒng)架構權衡也適用于電子情報(ELINT)、信號情報(SIGINT)和通信情報(COMINT)。此類系統(tǒng)一般有三種不同系統(tǒng)架構可供考慮(參見圖2)。

圖2A所示為最簡單的系統(tǒng)。 采用高線性度ADC,例如ADI公司的AD9265(其在70 MHz中頻輸入時具有93 dBc的SFDR和79 dBFS的信噪比(SNR),這種架構可提供出色的靈敏度和檢測性能,但最大采樣速率只有125 MSPS。這是以瞬時帶寬為代價而獲得的,不考慮抗混疊濾波器時的最大瞬時帶寬為62.5 MHz,通常要降低到40 MHz或更低。 系統(tǒng)中只有一個轉(zhuǎn)換器,系統(tǒng)成本很低,但射頻調(diào)諧器不得不以40 MHz的步幅掃描整個射頻帶寬,這會降低攔截某些信號的概率。

為了提高帶寬,一種顯而易見的方法是交錯使用多個高線性度、低采樣速率的轉(zhuǎn)換器,將其連接到單個寬帶射頻調(diào)諧器(圖2B),從而提高有效采樣速率和瞬時帶寬。 例如,若交錯使用8個AD9265 ADC,總有效采樣速率將達到1 GSPS,支持的瞬時帶寬接近500 MHz。 射頻調(diào)諧器只需以500 MHz的步幅掃描,因此射頻頻譜的偵測速度會快得多,攔截目標信號(尤其是捷變信號)的概率更高。另外,系統(tǒng)僅使用一個射頻調(diào)諧器,與圖2A相比,成本增加有限。

雖然這確實給射頻調(diào)諧器帶來更多難題(更寬的帶寬帶來的難題是要保持與前述架構相似的IP3和噪聲性能),但這種方法的主要不足是交錯ADC方面。 各轉(zhuǎn)換器在增益、直流失調(diào)和相位方面的失配,需要通過校準從系統(tǒng)中消除或利用數(shù)字信號處理加以管理,但即便這樣,SFDR、噪底或帶寬通常也會有一定的下降,導致此架構性能降低。 對于監(jiān)控帶寬內(nèi)的超高功率信號,系統(tǒng)可能不太敏感,使問題進一步惡化。 500 MHz頻段任意地方的這種信號都要求降低射頻和中頻增益,從而限制了低功率信號的攔截概率。

最高性能的架構如圖2C所示,其中實現(xiàn)了多個并行射頻與數(shù)字化儀子系統(tǒng),如果同樣使用AD9265,則可以同時觀測到多個相鄰40MHz頻段。 讓每個子系統(tǒng)偏移大約40 MHz(需要一些交疊),可以提高瞬時帶寬,但很顯然,這是以系統(tǒng)成本為代價,系統(tǒng)成本與瞬時帶寬成正比。與交錯方法相比,這種架構的好處是無需通過校準或數(shù)字信號處理來消除交錯引起的雜散。 此外,該系統(tǒng)抑制高功率阻塞或干擾的能力更強,因為各40 MHz頻段的射頻/中頻增益可以獨立設置。

圖2: 監(jiān)控系統(tǒng)架構選項

上述系統(tǒng)架構已在當今各種系統(tǒng)中采用,但如圖中所示,每種架構在性能、成本,還有可能是尺寸上存在限制。然而,最新的GSPS ADC可能很快就會打破現(xiàn)狀,這種ADC具備更高的線性度和嵌入式數(shù)字信號處理特性。AD9625和AD9680等新型ADC提供1.25 GSPS到2.5 GSPS的采樣速率,SFDR高達85 dBc。

GSPS ADC的線性度比不上低采樣速率的器件,但可以看出,差距正在縮小。使用單個GSPS ADC就能實現(xiàn)圖2B所示的架構,同時不會有交錯帶來的缺點。此外,更高的線性度可提高檢測靈敏度,并將干擾和阻塞的影響降至最小,縮小這種架構與圖2中圖2C所示系統(tǒng)的性能差距,而且成本更低,尺寸更小。

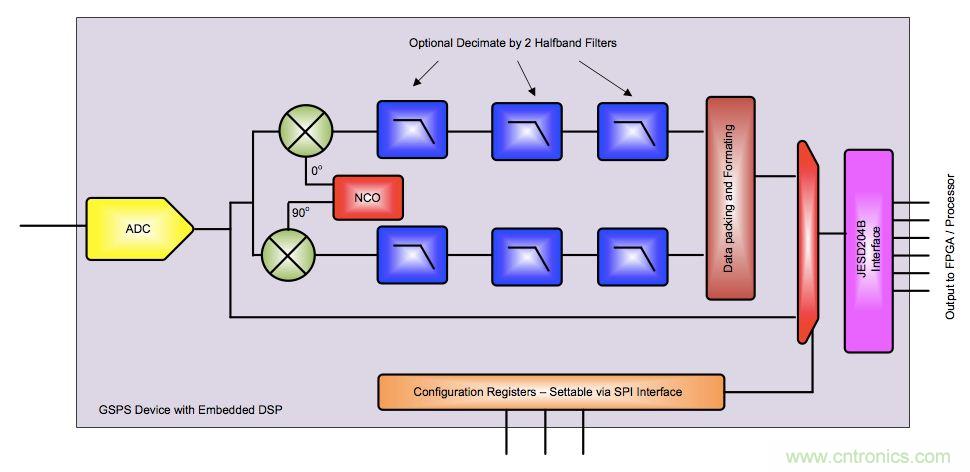

然而,雖然這一方面能促成新系統(tǒng)架構的出現(xiàn),但這些新器件更激動人心的方面是它們還能在轉(zhuǎn)換器的模數(shù)轉(zhuǎn)換級之后實現(xiàn)數(shù)字信號處理功能。65 nm CMOS工藝支持在轉(zhuǎn)換器中實現(xiàn)更高速度的數(shù)字信號處理。例如,AD9625和AD9680均實現(xiàn)了數(shù)字下變頻(DDC)功能,因而高速ADC可動態(tài)改變帶寬——從全帶寬到1,000MHz以上的數(shù)字化奈奎斯特頻段內(nèi)的可選子頻段。在圖3所示的架構中,2.5 GSPS、12位ADC AD9625帶有嵌入式DSP選項。

在寬帶模式下,這種ADC支持以1 GHz步幅監(jiān)控射頻頻譜,以便快速評估射頻圖景。 一旦確定目標信號,便可將此數(shù)據(jù)引導至DDC。DDC使用數(shù)字控制振蕩器(NCO)和濾波級,可從轉(zhuǎn)換器奈奎斯特頻段內(nèi)的任何地方選擇一個頻段,并進行8倍或16倍的數(shù)字抽取,從而進一步抑制噪底。雖然這一功能可以在器件中轉(zhuǎn)換器之后的數(shù)字信號處理級中輕松實現(xiàn),但在ADC本身中執(zhí)行有助于降低ADC的輸出數(shù)據(jù)速率,更重要的是,可以降低傳輸功耗。因此,使用DDC時,系統(tǒng)功耗顯著降低。

圖3: 帶可選且可旁路嵌入式數(shù)字下變頻器的2.5 GSPS ADC

航空航天和防務系統(tǒng)持續(xù)重視縮減尺寸、重量和功耗(SWaP),隨著GSPS領域的高速轉(zhuǎn)換器的線性度不斷提高,系統(tǒng)架構師開始探索新的選項。把數(shù)字信號處理集成到高速轉(zhuǎn)換器內(nèi)部后,一系列選項和系統(tǒng)優(yōu)化方法開始顯露出來,現(xiàn)階段因而成為新一代監(jiān)控系統(tǒng)開發(fā)的一個令人興奮的時期。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: