【導讀】在我們的日常工作中,電源管理對實現(xiàn)電子元件的進一步集成至關重要。數(shù)十年來,TI 致力于開發(fā)新的工藝、封裝和電路設計先進技術,從而為您的設計提供出色的電源器件。

無論您是需要提高功率密度、延長電池壽命、減少電磁干擾、保持電源和信號完整性,還是維持在高電壓下的安全性,我們都致力于幫您解決電源管理方面的挑戰(zhàn)。德州儀器 ( TI ) 是與您攜手推動電源進一步發(fā)展的合作伙伴。

本文將講解如何實現(xiàn)低噪聲和高精度:增強電源和信號完整性,以提高系統(tǒng)級保護和精度。

要實現(xiàn)精密信號鏈,低噪聲 LDO 穩(wěn)壓器和開關轉(zhuǎn)換器、精密的監(jiān)控和可靠的保護是必不可少的。對于電動汽車電池監(jiān)測、測試和測量以及醫(yī)療等應用,TI 使用專用的電源處理技術以及先進的電路和測試技術,可提高精度、更大限度地減少失真,并降低線性和開關電源轉(zhuǎn)換器的噪聲。

TI 低噪聲和高精度技術的優(yōu)勢

● 減少 IC 誤差源

● 系統(tǒng)噪聲消減

減少 IC 誤差源

(1)利用 TI 高度優(yōu)化的低噪聲互補金屬氧化物半導體 (CMOS) 工藝來減少工藝的非理想因素

(2)利用先進的電路和測試技術來降低工藝非理想因素的影響

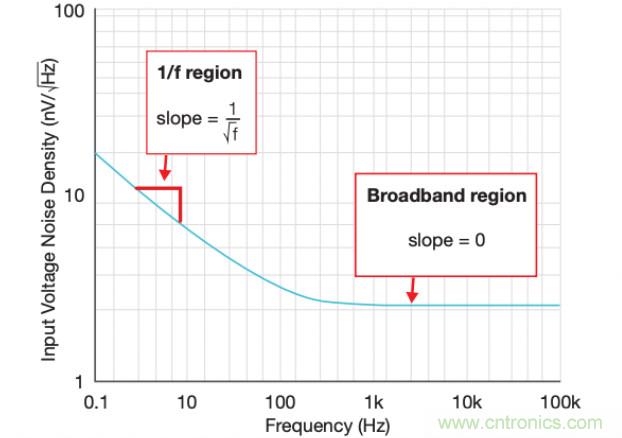

圖 1. 噪聲與頻率曲線圖

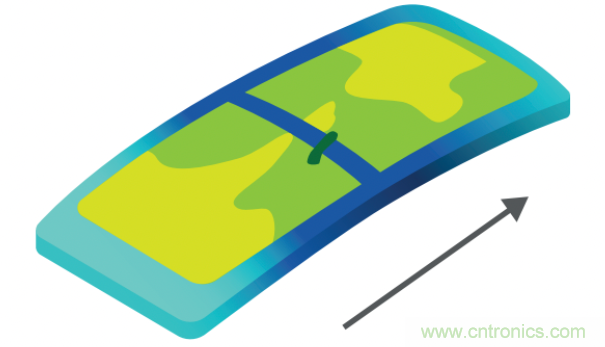

(3)采用了陶瓷封裝和電路板應力管理等先進技術

圖 2. 調(diào)節(jié)器件和電路板應力

系統(tǒng)噪聲消減

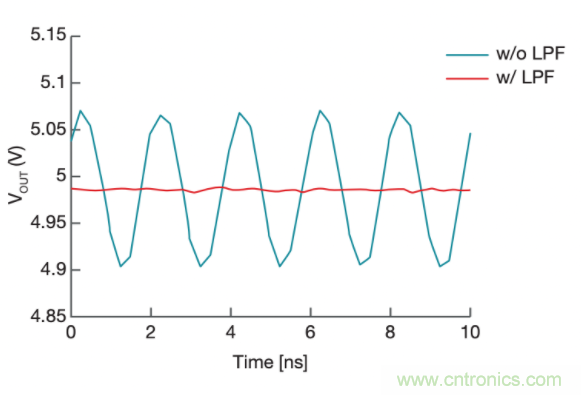

(1)技術的進步支持通過高電源抑制比 (PSRR) 低壓降穩(wěn)壓器 (LDO) 和片上濾波實現(xiàn)更高的系統(tǒng)級抗干擾和抗噪性能

圖 3. 高 PSRR 可實現(xiàn)更好的濾波

和更低的輸出噪聲

如何降低 LDO 噪聲?

LDO 中的主要噪聲源來自帶隙基準源,可使用兩種方法來降低 LDO 中的噪聲。下面內(nèi)容詳細說明了這兩種方法。

降低噪聲的一種方法是降低 LDO 帶寬,這可以通過降低 LDO 內(nèi)部誤差放大器的帶寬來實現(xiàn)。但是,如果我們降低誤差放大器的帶寬,則會降低 LDO 瞬態(tài)響應速度。

另一種方法是使用低通濾波器 (LPF)。我們知道,LDO 噪聲的最主要來源是內(nèi)部的帶隙基準源。因此,我們可在帶隙輸出和誤差放大器輸入之間插入一個 LPF,從而在誤差放大器將帶隙噪聲放大之前將其降低。通常,該 LPF由一個內(nèi)部大電阻器和一個外部電容器組成。此濾波器的截止頻率設置得越低越好,從而濾除幾乎所有的帶隙噪聲。

這里始終有一個問題:為什么占用大部分芯片面積的大功率導通元件(主要是 FET)不是主要噪聲源?答案是沒有增益。作為主要噪聲源的帶隙基準源連接至誤差放大器的輸入端,因此會被誤差放大器的增益放大。我們知道,要研究輸出噪聲,首先要了解運算放大器輸入的每個噪聲影響因素;所以,要研究導通 FET 的噪聲,需要先找到噪聲的影響因素,即導通 FET 和誤差放大器輸入之間的開環(huán)增益。開環(huán)增益非常大,因此,導通 FET 的其他噪聲影響因素通??梢院雎圆挥?。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: