【導讀】隨著電子技術(shù)的飛速發(fā)展,存儲器的種類日益繁多,每一種存儲器都有其獨有的操作時序,為了提高存儲器芯片的測試效率,一種多功能存儲器芯片的測試系統(tǒng)應運而生。

本文提出了一種多功能存儲器芯片的測試系統(tǒng)硬件設(shè)計與實現(xiàn),對各種數(shù)據(jù)位寬的多種存儲器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)進行了詳細的結(jié)口電路設(shè)計(如何掛載到NIOSII的總線上),最終解決了不同數(shù)據(jù)位寬的多種存儲器的同平臺測試解決方案,并詳細地設(shè)計了各結(jié)口的硬件實現(xiàn)方法。

引言

隨著電子技術(shù)的飛速發(fā)展,存儲器類芯片的品種越來越多,其操作方式完全不一樣,因此要測試其中一類存儲器類芯片就會有一種專用的存儲器芯片測試儀。本文設(shè)計的多種存儲器芯片測試系統(tǒng)是能夠?qū)RAM、Nand FLASH、Nor FLASH、MRAM、EEPROM等多種存儲器芯片進行功能測試,而且每一類又可兼容8位、16位、32位、40位等不同寬度的數(shù)據(jù)總線,如果針對每一種產(chǎn)品都單獨設(shè)計一個測試平臺,其測試操作的復雜程度是可想而知的。為達到簡化測試步驟、減小測試的復雜度、提高測試效率、降低測試成本,特設(shè)計一種多功能的存儲器類芯片測試系統(tǒng),實現(xiàn)在同一平臺下完成所有上述存儲器芯片的方便快捷地測試。

設(shè)計原理

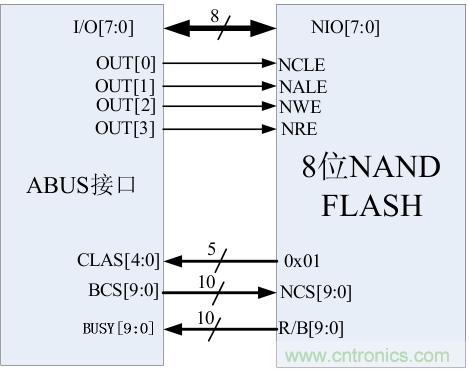

此設(shè)計方案根據(jù)上述各種存儲器獨自的讀寫時序訪問特性,通過FPGA的靈活編程特性,適當?shù)卣{(diào)整NIOSII的外部總線時序,最終實現(xiàn)基于NIOSII的外部總線訪問各種存儲器讀寫時序的精確操作。如圖2-1。通過FPGA自定義一個可以掛載所有存儲器芯片的總線接口-ABUS,如表1。而且在同一個接口上能夠自動識別各種接入的被測試存儲器芯片,它們通過類別輸入信號(CLAS)來區(qū)分,每一種存儲器芯片對應一種獨特的操作時序。下面是幾種存儲器芯片的接口連接方式及信號描述。其它的存儲器芯片都可以用類似的接法掛載到ABUS總線上,最終完成測試。

圖 2?1 NIOSII的總線掛載各類存儲器芯片連接示意圖

表1:ABUS接口信號說明表

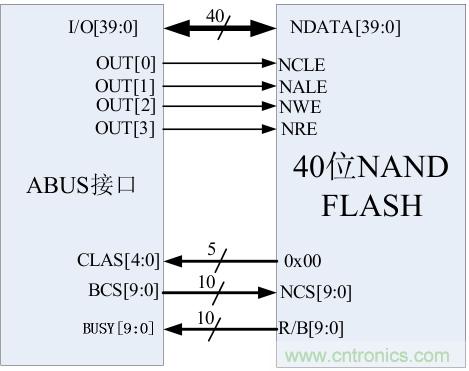

40位NAND FLASH連接設(shè)計

如圖2-2所示,40位NAND FLASH與NIOSII 通過ABUS(FPGA)橋接,把外部總線的時序完全轉(zhuǎn)換成NAND FLASH的操作時序。40位NAND FLASH芯片品由五個獨立的8位NAND FLASH芯片拼接構(gòu)成。5個8位器件的外部IO口拼接成40位的外部IO口,而各自的控制線(NCLE,NALE,NRE,NWE)連接在一起構(gòu)成一組控制線(NCLE,NALE,NRE,NWE),片選相互獨立引出成NCS0-NCS9,忙信號獨立引出為R/B0-R/B9。

如表2,詳述了40位NAND FLASH與ABUS的連接關(guān)系。

圖 2?2 ABUS與40位NAND FLASH接口圖

表2,40位NAND FLASH接口連接表

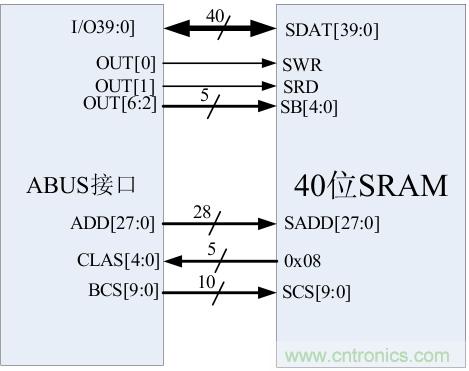

40位SRAM與NIOSII連接

40位SRM模塊與NIOSII通過ABUS連接,實現(xiàn)正確的時序讀寫操作。測試時,一次只測試8位,分5次完成所有空間的測試。如圖2-4。表4是詳細的信號連接說明。

圖 2?4 ABUS與40位SRAM連接

表4,40位SRAM接口連接表

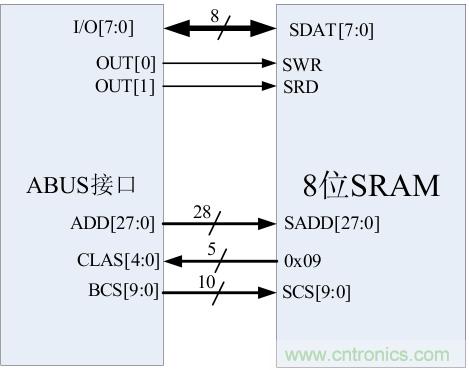

8位SRAM與NIOSII連接

8位SRM模塊與NIOSII通過ABUS(FPGA)連接,實現(xiàn)正確的時序讀寫操作。如圖2-5。表5是信號連接說明。

圖 2?5 ABUS與8位SRAM連接

8位SRAM與NIOSII連接

8位SRM模塊與NIOSII通過ABUS(FPGA)連接,實現(xiàn)正確的時序讀寫操作。如圖2-5。表5是信號連接說明。

圖 2?5 ABUS與8位SRAM連接

表5,8位SRAM接口連接表

硬件電路設(shè)計

在測試NAND FLASH時,測試時間長達十個小時不等。在此為提高測試效率,增加測試速度,本設(shè)計采用兩套完全一樣且獨立的硬件系統(tǒng)構(gòu)成??赏瑫r最多測試2片NAND FLASH器件。每一個硬件系統(tǒng)由一個微處理器(NIOSII)加一個大容量FPGA及一個存儲器測試擴展接口(即ABUS接口)三大模塊構(gòu)成。如圖3-1。RS232通信接口實現(xiàn)測試系統(tǒng)與上位機的數(shù)據(jù)交換,完成人機交互操作。電源系統(tǒng)產(chǎn)生各種合適的電壓,滿足各芯片的電源供給。

圖 3?1 硬件方塊圖

處理器模塊電路

處理器模塊電路由FPGA內(nèi)嵌的NIOSII軟核(CPU)、兩路RS232通信、一個FLASH芯和一個SRAM芯片組成。CPU是整個系統(tǒng)的核心管理者,向下負責各種存儲器芯片的讀寫測試,向上負責與上位機通信,實現(xiàn)人機交互。通信由其中一個RS232電路完成,另一個RS232電路用來實現(xiàn)系統(tǒng)調(diào)試和軟件固化。FLASH芯片用來存儲程序代碼及重要的數(shù)據(jù)。而SRAM芯片在CPU上電工作以后,通過CPU加載FLASH的程序,最終給CPU的程序代碼提供快速的運行環(huán)境。

基于FPGA的ABUS接口模塊

ABUS接口模塊由FPGA芯片、配置FLASH及數(shù)據(jù)存儲EEPROM芯片構(gòu)成。ABUS要實現(xiàn)NIOSII的外部總線與多種存儲器模塊的接口對接,每一種特定的存儲器有一個特定的時序邏輯,而每一種時序邏輯可以通過FPGA的硬件代碼(IP核)來實現(xiàn),具體的每一個存儲器模塊在測試時會給ABUS接口一個固定的類別信號CLAS,ABUS接口根據(jù)這個類別信號識別出各種SIP存儲器模塊,最終切換出正確的對應特定產(chǎn)品的時序邏輯,來完成NIOSII通過外部總線來對存儲器芯片的讀寫測試。而配置FLASH實現(xiàn)FPGA在上電時硬件程序的加載工作及掉電數(shù)據(jù)保護。EEPROM用來存儲一些重要的系統(tǒng)參數(shù)。

SIP存儲器測試擴展接口

存儲器測試擴展接口在硬件上由兩排雙排座構(gòu)成。一共是120個管腳。ABUS接口與測試擴展接口相連接:40個管腳與雙向的數(shù)據(jù)或I/O線相連、8個管腳與8根信號輸入控制線相連、16個管腳與16根片選信號輸出線相連、5個管腳與5根類別輸入信號相連、16個管腳與16根狀態(tài)輸入信號線相連、27個管腳與27根地址線相連。其它的管腳可分配成電源和地線,以及信號指示等。

ABUS接口IP核的設(shè)計

每一種SIP存儲器對應于一個特定的ABUS接口IP核,以實現(xiàn)正確的時序讀寫操作。這個IP核有一個統(tǒng)一的接口約定,都是由兩個固定的接口構(gòu)成,其中與NIOSII連接的是外部總線接口,其操作按照NIOSII的外部總線時序規(guī)范來實現(xiàn),另一個接口就是上文提及的ABUS接口,在相應的CLAS信號有效的情況下,它負責把NIOSII的外部總線讀寫時序轉(zhuǎn)換成對應存儲器芯片的時序。IP核的工作就是完成這些讀寫操作的轉(zhuǎn)換。表5是各種SIP存儲器對應的類別信(CLAS)號輸入值,在設(shè)計接口轉(zhuǎn)接板時要按這個值設(shè)定,ABUS才會切換出正確的讀寫時序。

七位類別示別信號含義:T_XX_WW_CC,T為1表示高低測試測試,為0表示常溫下的功能測試。XX表示存儲器種類,WW表示總線寬度,CC表示容量種類。

表5 各種SIP存儲器對應的CLAS信號值

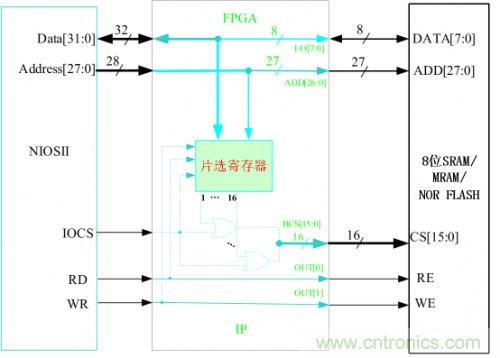

8位SRAM/MRAM/NOR FLASH接口IP核設(shè)計

如圖4-1,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的總線時序完全滿足。故在FPGA內(nèi)部只要簡單地把相應的控制線和數(shù)據(jù)線相連就可以了,唯獨只要設(shè)計一個片選寄存器,用來區(qū)分存儲器芯片的16個片選。每一個片選可以訪問的空間為128MByte。片選寄存器的地址為(基址+0x0FFFFFFC),基地址設(shè)在NIOSII外部總線的最高地址位。

圖 4?1 8位SRAM/MRAM/NOR FLASH接口IP

16位SRAM/MRAM/NOR FLASH接口IP核設(shè)計

如圖4-2,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的總線時序完全滿足。故在FPGA內(nèi)部只要簡單的把相應的控制線和數(shù)據(jù)線相連就可以了,唯獨只要設(shè)計一個片選寄存器,用來區(qū)分SIP的16個片選。每一個片選可以訪問的空間為128MByte。片選寄存器的地址為(基址+0x0FFFFFFC),基地址設(shè)在NIOSII 外部總線的最高地址位。

圖 4?2 16位SRAM/MRAM/NOR FLASH接口IP

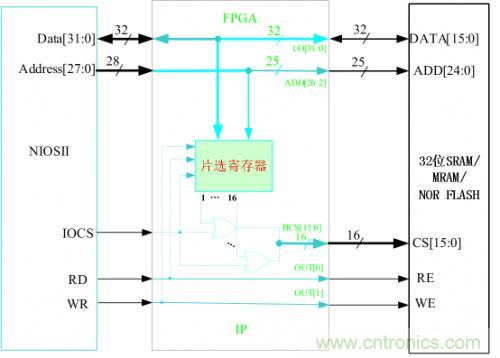

32位SRAM/MRAM/NOR FLASH接口IP核設(shè)計

如圖4-3,SRAM、MRAM和NOR FLASH的接口操作基本一致,NIOSII的總線時序完全滿足。故在FPGA內(nèi)部只要簡單的把相應的控制線和數(shù)據(jù)線相連就可以了,唯獨只要設(shè)計一個片選寄存器,用來區(qū)分SIP的16個片選。每一個片選可以訪問的空間為128MByte。片選寄存器的地址為(基址+0x0FFFFFFC),基地睛設(shè)在NIOSII 外部總線的最高地址位。

圖 4?3 32位SRAM/MRAM/NOR FLASH接口IP

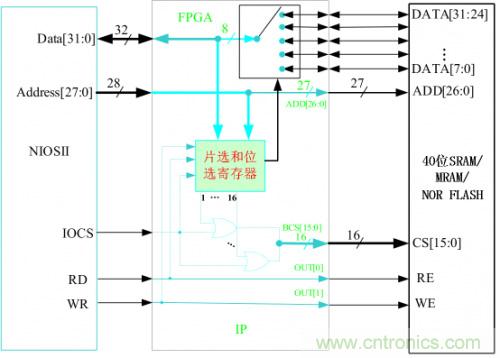

40位SRAM/MRAM/NOR FLASH接口IP核設(shè)計

如圖4-4,40位的數(shù)據(jù)寬度有點特殊。在此我們把40位的數(shù)據(jù)分成5個8位的區(qū)域,用8位寬度的總線去分別訪問每一個區(qū)域。IP核中的位選寄存器就是用來完成切換8位數(shù)據(jù)總線到40位總線的5個區(qū)域的其中一個。片選寄存器的地址為(基址+0x0FFFFFFC),位選寄存器的地址為(基址+0x0FFFFFF8)。最大可以測試128M×40位×16片的存儲器SRAM/MRAM/NOR FLASH模塊。

圖 4?4 40位SRAM/MRAM/NOR FLASH接口IP

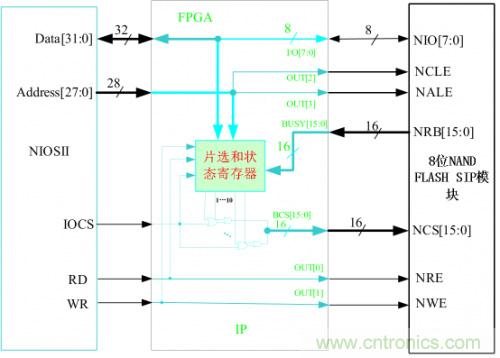

8位NAND FLASH的ABUS接口IP設(shè)計

如圖4-5,通過寫片選寄存器來選中模塊的16個片選的其中一個。我們約定其地址為(基址+0x0FFFFFFC)。讀狀態(tài)寄存器返回的是16個NAND FLASH芯片的忙信號,其地址為(基址+0x0FFFFFF8)。向地址(基址+0x00)寫入數(shù)據(jù)就是對NAND FLASH數(shù)據(jù)寄存器的寫操作。向地址(基址+0x00)單元讀數(shù)據(jù)就是對NAND FLASH數(shù)據(jù)寄存器的讀操作。向地址(基址+0x01)寫入數(shù)據(jù)就是對NAND FLASH命令寄存器的寫操作。向地址(基址+0x02)寫入數(shù)據(jù)就是對NAND FLASH地址寄存器的寫操作。

圖 4?5 8位NAND FLASH的ABUS接口IP核設(shè)計圖

16位NAND FLASH的ABUS接口IP設(shè)計

16位的NAND FLASH存儲器芯片可以有多種組合方式,可以用多個16位的NAND FLASH組合,也可以用多個8位的NAND FLASH組合。這里我們假設(shè)16位的SIP NAND FLASH產(chǎn)品是由多個16位的NAND FLASH組合而成,下面的IP核是根據(jù)它的結(jié)構(gòu)來設(shè)計的。

如圖4-6,通過寫片選寄存器來選中模塊的16個片選的其中一個。我們約定其地址為(基址+0x0FFFFFFC)。讀狀態(tài)寄存器返回的是16個NAND FLASH芯片的忙信號,其地址為(基址+0x0FFFFFF8)。向地址(基址+0x00)寫入數(shù)據(jù)就是對NAND FLASH數(shù)據(jù)寄存器的寫操作。向地址(基址+0x00)單元讀數(shù)據(jù)就是對NAND FLASH數(shù)據(jù)寄存器的讀操作。向地址(基址+0x01)寫入數(shù)據(jù)就是對NAND FLASH命令寄存器的寫操作。向地址(基址+0x02)寫入數(shù)據(jù)就是對NAND FLASH地址寄存器的寫操作。

圖 4?6 16位NAND FLASH的ABUS接口IP核設(shè)計圖

驗證與總結(jié)

將寫好的FPGA程序和調(diào)試的C代碼寫入FLASH后,掉電重配置FPGA,串口的輸出能正常識別所有設(shè)置好的存儲器芯片,并能夠進行準確地讀寫功能測試。達到了設(shè)計目的。

本文介紹了一種低成本、簡單、靈活的多種存儲器芯片測試系統(tǒng)的硬件設(shè)計,并采用FPGA、FLASH、SDRAM、RS232電路等實現(xiàn)。采用這種方案,用戶可根據(jù)市場需求,靈活的增加測試系統(tǒng)功能,實現(xiàn)更多的存儲器芯片測試。