【導讀】對于很多初學PCB設計的人員來說,高速信號是神秘的,設計人員可能更多關注的是怎么布局,怎么調整布線拓撲,怎么把信號走通,對信號仿真模型更是了解的不多。

而對于初學仿真的小伙伴們,則可能從學習傳輸線開始,需要了解高速信號是怎么傳輸的,要學習反射,串擾,端接,匹配,損耗……然而,當我們真正準備仿真一個DDR信號質量時,卻是從學會調用IBIS模型開始的。

我們在接到仿真項目時,總是免不了要向客戶索要芯片模型。俗話說:巧婦難為無米之炊。沒有米,是不可能做出香噴噴的米飯的,沒有準確的芯片模型,我們的仿真就無法進行。 在仿真分析中,最常見的模型就是IBIS模型了。小編這篇文章不是要介紹怎么去使用IBIS,也不是要去闡述 IBIS是怎么得來的,只是先讓初學者對IBIS有一個感性的認識。

進入正題。我們知道IBIS模型是行為級模型,它描述了芯片的輸入輸出狀態(tài),它不同于Spice模型,不會泄露芯片內部的電路結構。

首先,讓我們來思考一下仿真分析為什么需要IBIS模型。

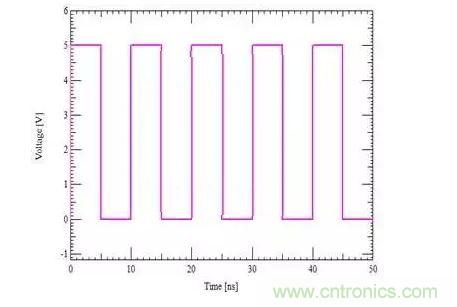

從根源說起。在數字電路中,芯片與芯片之間傳輸的是數字信號,數字信號是0、1這樣的脈沖信號。完美的數字信號應該是圖一這樣的,它的上升時間和下降時間幾乎為零

圖一

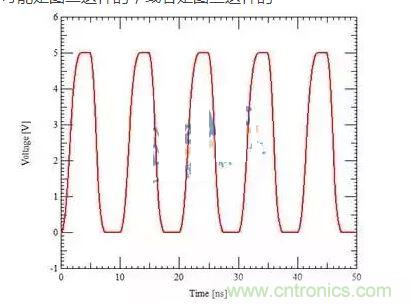

但實際傳輸的信號,可能是圖二這樣的,或者是圖三這樣的

圖 三

我們可以看到,上圖這些信號都是幅值為5V的脈沖,頻率為100M,但是它們的特點不一樣。圖二波形的上升沿很陡峭,圖三波形的上升沿卻很平緩。

實際應用中,我們使用的芯片也是這樣,不同芯片輸出的波形也不一樣。它們不僅周期頻率不同,上升時間、幅值也會不同。

先來了解一下芯片的構造??磥碜鰹橐幻鸖I工程師,需要學習和掌握的東西還真不少。不光是關注傳輸線外部互連,還需要學習很多芯片知識。

我們姑且認為IC芯片由三部分組成: Core、Buffer和封裝。Core是芯片內部的核心邏輯電路,工作電壓較低,驅動能力也低。Buffer是終端接口電路,電源電壓一般較高,驅動能力較強,是core和其他IC之間的連接橋梁,封裝則是連接Buffer和外部器件的金線和管腳。芯片核心與核心之間的通信就是通過buffer、封裝和傳輸線來完成的。Buffer和封裝是外圍電路能“看見”的部分。就是說芯片內的指令是由core來發(fā)出的,至于指令是以什么形式,以多高的電壓來表現,這就要看 Buffer來發(fā)揮作用了。

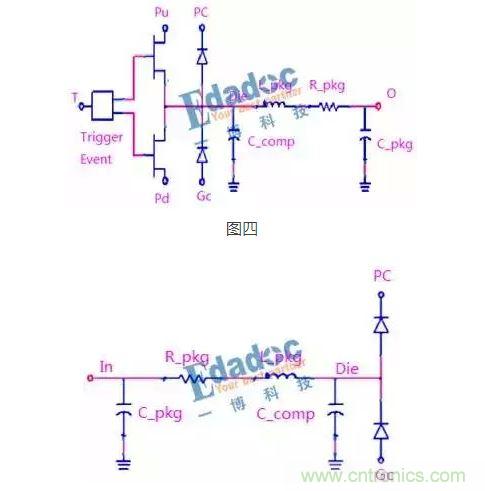

說到Buffer,那么Buffer究竟是什么呢?就像傳輸線可以用分布模型RLGC來定義,Buffer也可以用一些等效電路來描述。IBIS里面的Buffer有Input Buffer,Output Buffer,Input/Output Buffer等類型。

[page]

下圖就是Buffer和封裝的等效電路,圖四是Output buffer,圖五是Input Buffer。這里要強調一下,下圖是包含了Buffer和封裝的,圖四右邊部分是封裝等效電路。圖五左邊部分是封裝等效電路。我們需要明白的是IBIS模型是考慮了封裝的影響的。小編的模電學的不是很好,不想去詳細分析這些器件是怎么工作的。

圖五

那么仿真時調用不同的IBIS模型有什么區(qū)別呢?我們調用實際的IBIS模型來仿真一下,看看仿真時調用不同的IBIS模型之間到底有什么區(qū)別。

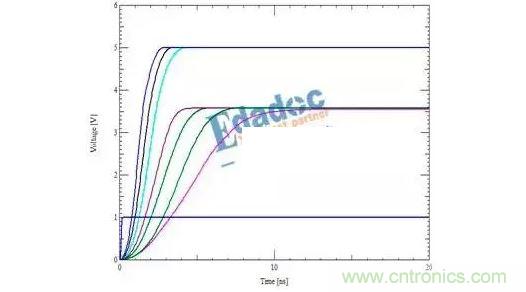

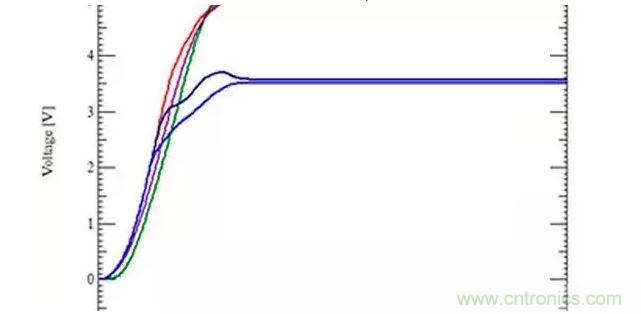

首先來挑選幾個不同的IBIS模型,加載一個上升沿,輸出的結果如圖六:

圖六

上圖這些上升沿的上升邊陡峭程度不一樣,對應的幅值也不一樣??梢?,調用不同的模型,同樣是一個上升沿,會有這么多的表現形式。

我們再來看看接收端模型對信號有什么影響。驅動端加載一個上升沿,輸入到輸出之間的線很短,可以忽略傳輸線對信號的影響。終端調用了不同的Input模型,結果如下圖七。

圖七

仿真時,驅動端加載的是5V上升沿信號。接收端接收的電壓有5V,3.3V。同樣的輸入,但是在終端接收的電壓不一樣。對于供電電壓是3.3V的接收端器件,就算驅動電壓是5V,它也會在保護二極管的作用下,最終電壓被拉回到3.3V。而對于供電電壓本來就是5V的器件,調用不同的Input buffer模型對信號波形的影響是比較小的。這里我們就明白了,為什么在仿真中,如果我們不能準確找到接收芯片模型,可以用類似的模型去替代。

通過仿真我們了解到,Buffer本身并不能產生信號波形,它本身是個被動器件,只是起驅動的作用。我們在仿真的時候自己會定義各種碼型,碼型只是定義一種邏輯關系而已,至于這種邏輯關系是以什么形式表現出來,就要看芯片的Buffer了。在仿真中,我們想要知道主控芯片輸出的波形長什么樣,那就要借助我們的IBIS模型了。

以上是我對IBIS模型的一點認識,歡迎討論。