【導讀】此方案主要由兩個部分組成:編碼板和解碼板的開發(fā)以及調試。目前,編碼板與解碼板可協(xié)同工作。編碼板的作用是完成拍攝數(shù)據(jù)的無損存儲和實時壓縮,而解碼板是完成壓縮數(shù)據(jù)的實時解碼和PC回放。

方案名稱:寬幅圖像存儲、壓縮與回放系統(tǒng)的研制與開發(fā)。

關鍵技術及創(chuàng)新點:

本項目關鍵技術之一是高速大容量存儲通道的設計,該設計摒棄了當前廣泛采用的由操作系統(tǒng)控制硬盤進行存儲的模式,轉而采用FPGA在硬件底層上直接對硬盤進行控制,同時輔以SDRAM作為大容量高速數(shù)據(jù)緩存,極大地提高了硬盤的存儲速率。本系統(tǒng)設計的另一亮點,即采用數(shù)據(jù)傳輸與數(shù)據(jù)壓縮并行工作的方式,實現(xiàn)壓縮碼流傳輸時間的復用,極大提高了系統(tǒng)效率。在該方式下,數(shù)據(jù)發(fā)送任務由FPGA實現(xiàn),縮短了DSP在數(shù)據(jù)發(fā)送任務上的時間開銷,做到了圖像壓縮和數(shù)據(jù)傳送的并行操作,對相機拍攝間隔時間的縮短起到了主要的作用。

技術成熟性和可靠性:

在硬件設計上,本項目在設計之初便考慮了系統(tǒng)可靠性問題,對編碼板和解碼板采用鏡像設計方法,使得系統(tǒng)調試更為簡便,同時也增強了系統(tǒng)的可靠性。在軟件設計上,以FIFO為基礎的接口同步方案以及乒乓操作等數(shù)據(jù)緩存技術的使用,提高了軟件在數(shù)據(jù)處理方面的可靠性。同時,基于FPGA的SDRAM、ATA外圍存儲設備控制在本小組所在實驗室已是成熟技術。我們對系統(tǒng)連續(xù)進行200次拍照存儲壓縮試驗,所測數(shù)據(jù)完全正確,這從一個側面驗證了系統(tǒng)的可靠性。

方案基本功能框圖及描述:

1.數(shù)據(jù)存儲、壓縮和傳輸部分

① 數(shù)據(jù)存儲

寬幅圖像數(shù)據(jù)量龐大,單幅圖像約20MB,數(shù)據(jù)存儲介質采用ATA接口標準的固態(tài)硬盤。現(xiàn)行ATA接口標準在PIO模式下的存儲速率理論值為16.7MB/s,而CCD提供的數(shù)字接口速率約為25MHz,因此,系統(tǒng)采用SDRAM作為圖像緩存。在硬件結構上,SDRAM和硬盤均由FPGA控制,該模塊實現(xiàn)了一條完整的高速大容量存儲通道,可在2秒內完成單幅原始圖像數(shù)據(jù)的存儲。

② 數(shù)據(jù)壓縮

由于數(shù)據(jù)傳輸采用RS422接口,傳輸速率有限,不能直接將原始數(shù)據(jù)進行傳輸,因此需要進行圖像壓縮。系統(tǒng)采用專用JPEG2000壓縮芯片ADV202,在DSP控制下讀取硬盤數(shù)據(jù),對圖像進行分塊壓縮。

③ 數(shù)據(jù)傳輸

數(shù)據(jù)傳輸采用RS422接口,傳輸速率2Mb/s,在圖像壓縮比10:1的情況下,單幅圖像壓縮碼流傳輸時間約8s。本系統(tǒng)采用數(shù)據(jù)傳輸與數(shù)據(jù)壓縮并行工作的方式,實現(xiàn)壓縮碼流傳輸時間的復用,極大提高了系統(tǒng)效率。在該方式下,DSP操做ADV202對圖像進行分塊壓縮,并將當前分割圖像壓縮數(shù)據(jù)快速傳達SRAM,隨后,F(xiàn)PGA操作SRAM從中讀出數(shù)據(jù),并按RS422接口標準發(fā)送。事實上,在FPGA進行數(shù)據(jù)傳輸?shù)耐瑫r,DSP已經開始下一分割圖像的壓縮。這其實是資源與速度互換原則的體現(xiàn)。

2.圖像回放部分

① 數(shù)據(jù)接收

數(shù)據(jù)接收主要由FPGA控制完成,有兩大任務,一是將有效數(shù)據(jù)從傳輸幀結構中提取出來,二是將壓縮圖像數(shù)據(jù)和系統(tǒng)參數(shù)數(shù)據(jù)分離。實現(xiàn)時,F(xiàn)PGA控制兩片SRAM乒乓操作實現(xiàn)壓縮數(shù)據(jù)的接收,其中每片SRAM負責存放一幅完整的圖像壓縮數(shù)據(jù),保證輸入數(shù)據(jù)流和輸出數(shù)據(jù)流連續(xù)不斷,使得數(shù)據(jù)接收更加高效、穩(wěn)定。

② 數(shù)據(jù)解壓

數(shù)據(jù)解壓部分整體上同數(shù)據(jù)壓縮部分成鏡像關系,采用專用的JPEG2000壓縮芯片ADV202,在DSP的控制下讀取存儲在SRAM中的壓縮圖像數(shù)據(jù),對圖像進行分塊解壓。

③ 數(shù)據(jù)回放

數(shù)據(jù)回放部分主要通過PCI接口將圖像解壓數(shù)據(jù)和系統(tǒng)參數(shù)傳至PC進行顯示。PCI接口由PCI9054實現(xiàn),在PCI局部總線端采用Scatter/Gather DMA模式接收數(shù)據(jù)。PCI DMA傳輸時序和DSP并不兼容,因此,同步數(shù)據(jù)接口采用FIFO存取方法,通過FPGA實現(xiàn)從DSP到PCI數(shù)據(jù)接收端口的時序轉化。

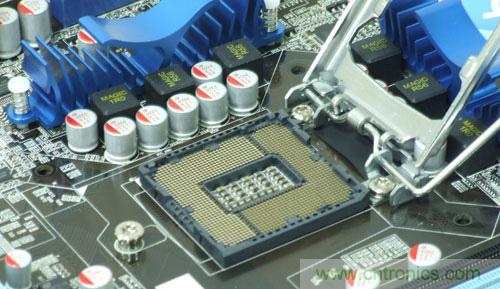

以FPGA為樞紐的硬件平臺開發(fā)需要FPGA具有豐富的IO引腳和足夠的邏輯資源。本項目在Spartan3系列的FPGA下進行開發(fā),開發(fā)軟件包括ISE8.2,ChipScope以及ModelSim等。

小編推薦閱讀:

我愛快包——電子工程師的外快錢包