【導(dǎo)讀】Intel 14nm工藝的過人之處大家有目共睹,但是和其他的相比又如何呢?日本同行PCWatch近日對(duì)Intel新工藝做了一番解析,更加凸顯了世界第一芯片巨頭的強(qiáng)悍。

我們?cè)敿?xì)了解過Intel 14nm工藝的過人之處,但那基本只是單一的介紹,沒有和其他廠商、其他工藝的正面對(duì)比。日本同行PCWatch近日也對(duì)Intel新工藝做了一番解析,更加凸顯了世界第一芯片巨頭的強(qiáng)悍。

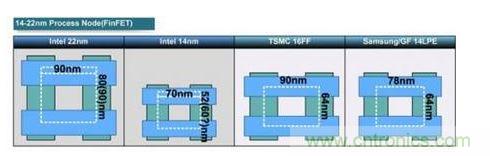

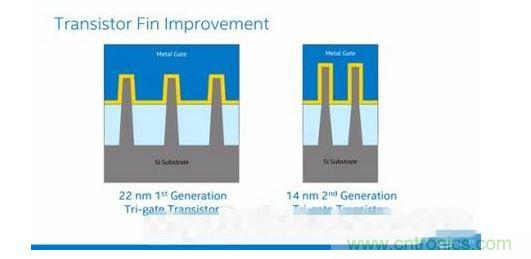

Intel 22nm工藝已經(jīng)率先使用了3D立體晶體管,14nm上將進(jìn)化到第二代,其他廠商則會(huì)陸續(xù)上馬類似的FinFET,包括臺(tái)積電16nm、三星/GlobalFoundries14nm。

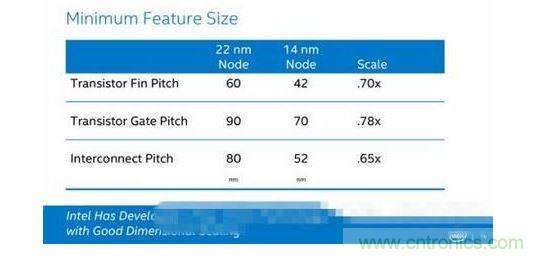

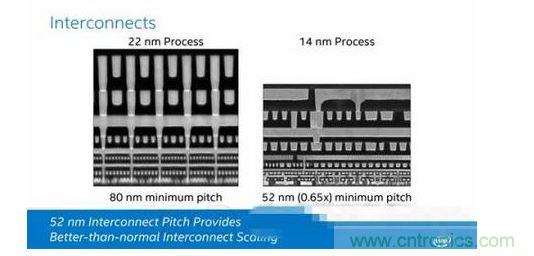

來看看幾個(gè)工藝的間距數(shù)據(jù):

Intel 14nm的柵極間距為70nm,內(nèi)部互聯(lián)最小間距為52nm,這兩項(xiàng)指標(biāo)分別比22nm縮小了22%、35%。

相比之下,臺(tái)積電16nm、三星/GF 14nm的柵極間距分別是90nm、78nm,前者只相當(dāng)于Intel 22nm的水平,后者也略弱一些,而內(nèi)部互聯(lián)最小間距則都是64nm,相比于Intel大了23%。

這些間距越小,就可以把晶體管做得更小、更密,對(duì)于電路集成度、芯片性能的重要性不言而喻。

Intel 14nm工藝的過人之處

Intel曾經(jīng)自己高調(diào)宣揚(yáng)過,整個(gè)世界也都承認(rèn),無與倫比的先進(jìn)制造工藝是這家芯片巨頭永遠(yuǎn)令人眼紅的優(yōu)勢。14nm工藝雖然從年初拖到了年底,但到時(shí)候仍然是這個(gè)地球上最先進(jìn)的。其他半導(dǎo)體企業(yè)紛紛減緩腳步或者合縱連橫的同時(shí),Intel仍在堅(jiān)持獨(dú)行,仍在引領(lǐng)世界。

隨著Broadwell-Y CoreM系列初步揭開面紗,Intel也公布了14nm工藝的大量相關(guān)資料,介紹了它的發(fā)展情況和技術(shù)優(yōu)勢。

簡單地說:

1、Intel 14nm工藝已經(jīng)通過各項(xiàng)驗(yàn)證,并在美國俄勒岡、亞利桑那工廠投入了量產(chǎn),明年還會(huì)加入愛爾蘭工廠。

2、它使用了第二代Tri-Gate(FinFET)立體晶體管技術(shù),擁有業(yè)界領(lǐng)先的晶體管性能、功耗、密度和成本。

3、Broadwell家族將首先采用14nm工藝制造,其后陸續(xù)擴(kuò)展到Intel各條處理器產(chǎn)品線。

4、Intel 14nm不但自己用,還會(huì)為很多客戶代工大量產(chǎn)品,從高性能到低功耗均可(已拿下Altera、松下)。

事實(shí)上,14nm也是迄今為止Intel面臨的最艱難的挑戰(zhàn),Intel對(duì)此也是很坦誠,并沒有遮遮掩掩。根據(jù)官方數(shù)據(jù),14nm工藝良品率初期低得要命,直到今年第二季度末才達(dá)到量產(chǎn)標(biāo)準(zhǔn),預(yù)計(jì)2015年第一季度才能追上22nm的水平,后者迄今仍是Intel良品率最高的工藝。

[page]

也只有到了2015年上半年,14nm的良品率、產(chǎn)能兩個(gè)關(guān)鍵指標(biāo)才能都滿足多條產(chǎn)品線的需求。這也正是Broadwell為什么首發(fā)只有一個(gè)超低壓版的CoreM系列,更多產(chǎn)品明年才會(huì)發(fā)布的根本原因。

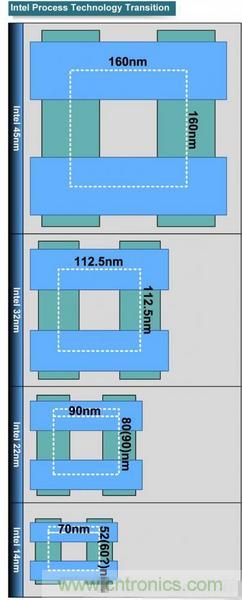

下邊繼續(xù)跟隨Intel的幻燈片,一起看看14nm工藝的神氣,尤其是和現(xiàn)有的22nm好好對(duì)比對(duì)比。

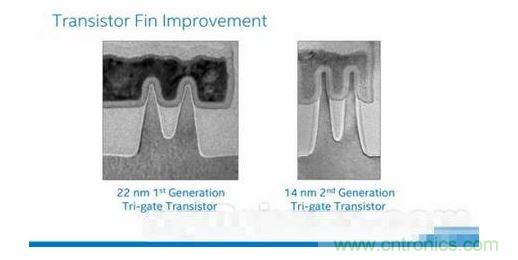

22nm上率先引入了Tri-Gate三柵極立體晶體管技術(shù),堪稱半導(dǎo)體歷史上的一次革命。雖然帶來了晶體管密度等方面的一些問題,導(dǎo)致核心面積過小、發(fā)熱密度升高,但仍然是大勢所趨,其他廠商紛紛引入,不過在名字上都叫做FinFET,異曲同工。

晶體管鰭片是最能反應(yīng)該技術(shù)進(jìn)步的地方。鰭片高度從34nm增至42nm(進(jìn)步比例24%),更高更薄可以改善驅(qū)動(dòng)電流、性能;間距從60nm縮小到42nm(進(jìn)步比例30%),可以提高集成密度;整體所需鰭片數(shù)量減少,可以改進(jìn)集成密度、降低電容。

另外,晶體管柵極間距、互聯(lián)間距也分別縮小到了70nm、52nm,進(jìn)步比例為22%、35%。

鰭片外圍覆蓋著的(黃色)就是金屬柵極。

層連最小間距也從80nm來到了52nm(進(jìn)步比例35%)。

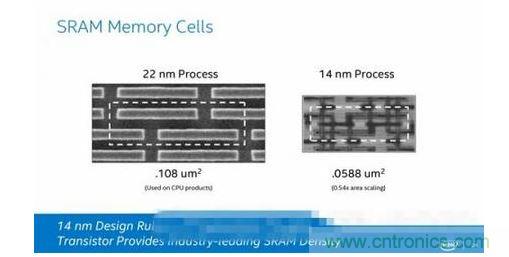

SRAM存儲(chǔ)單元的面積,上代是0.108平方微米,現(xiàn)在僅為0.0588平方微米,進(jìn)步比例達(dá)46%,幾乎縮小了一半。