【導(dǎo)讀】嵌入式FPGA(eFPGA)將在這類芯片中扮演重要角色。如為了滿足第六條中提到的車輛外部360度視頻監(jiān)控?cái)?shù)據(jù)的獲取和處理,采用eFPGA來設(shè)計(jì)相關(guān)功能芯片具有很明顯的優(yōu)勢。

2018年4月11日,工業(yè)和信息化部、公安部和交通運(yùn)輸部聯(lián)合發(fā)布“關(guān)于印發(fā)《智能網(wǎng)聯(lián)汽車道路測試管理規(guī)范(試行)》的通知”,為我國智能網(wǎng)聯(lián)汽車道路測試提供了相關(guān)法律依據(jù)。三部委在賦予智能網(wǎng)聯(lián)汽車上路資格的同時(shí),也提出了若干嚴(yán)格的條件。

其中,在第二章“測試主體、測試駕駛?cè)思皽y試車輛”的第七條第(四)點(diǎn)中,三部委要求:具備車輛狀態(tài)記錄、存儲及在線監(jiān)控功能,能實(shí)時(shí)回傳下列第1、2、3項(xiàng)信息,并自動記錄和存儲下列各項(xiàng)信息在車輛事故或失效狀況發(fā)生前至少90秒的數(shù)據(jù),數(shù)據(jù)存儲時(shí)間不少于3年:

1.車輛控制模式;

2.車輛位置;

3.車輛速度、加速度等運(yùn)動狀態(tài);

4.環(huán)境感知與響應(yīng)狀態(tài);

5.車輛燈光、信號實(shí)時(shí)狀態(tài);

6.車輛外部360度視頻監(jiān)控情況;

7.反映測試駕駛?cè)撕腿藱C(jī)交互狀態(tài)的車內(nèi)視頻及語音監(jiān)控情況;

8.車輛接收的遠(yuǎn)程控制指令(如有);

9.車輛故障情況(如有)。

由此可以看出,上述條件除了對進(jìn)行道路測試的智能網(wǎng)聯(lián)汽車有若干功能性要求外,還在相關(guān)領(lǐng)域?qū)⑼苿尤舾尚乱淮ㄐ?、監(jiān)控、控制和存儲等技術(shù)的發(fā)展,為智能網(wǎng)聯(lián)汽車專用SoC的開發(fā)提供新的市場機(jī)會。

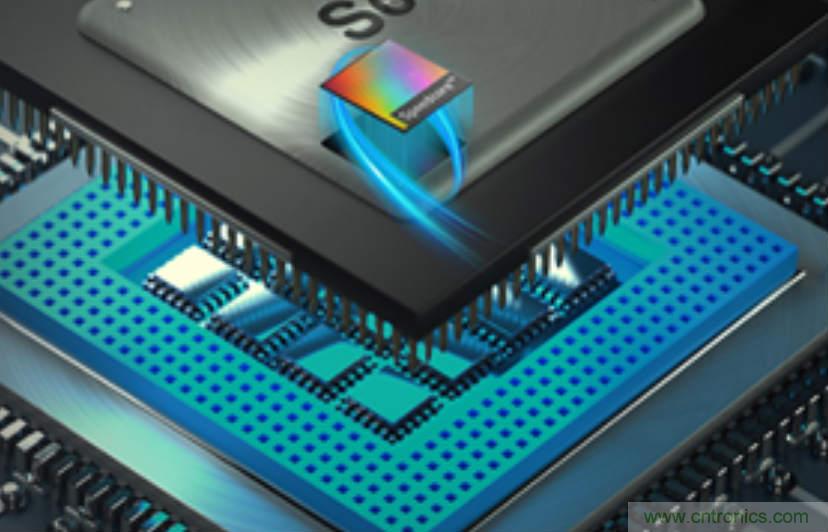

嵌入式FPGA(eFPGA)將在這類芯片中扮演重要角色。如為了滿足第六條中提到的車輛外部360度視頻監(jiān)控?cái)?shù)據(jù)的獲取和處理,采用eFPGA來設(shè)計(jì)相關(guān)功能芯片具有很明顯的優(yōu)勢。作為同時(shí)提供獨(dú)立FPGA芯片和eFPGA IP產(chǎn)品的公司,Achronix可以幫助智能汽車SoC設(shè)計(jì)人員先在FPGA芯片上開發(fā)和調(diào)試相關(guān)功能,而在市場進(jìn)入批量化應(yīng)用后無需顯著修改設(shè)計(jì),立即將設(shè)計(jì)移植到搭載了eFPGA的SoC之上。

有關(guān)eFPGA如何支持嵌入式360度視域視覺系統(tǒng)設(shè)計(jì),請閱讀Achronix Semiconductor資深產(chǎn)品營銷經(jīng)理Alok Sanghavi的文章,標(biāo)題為“將eFPGA應(yīng)用于嵌入式360度視域視覺系統(tǒng)中”。

帶有多個高分辨率攝像頭的嵌入式360°視域視覺系統(tǒng)已經(jīng)進(jìn)入了各種應(yīng)用中,如汽車傳感器融合、視頻監(jiān)控、目標(biāo)檢測、運(yùn)動分析等。在此類系統(tǒng)中,多個實(shí)時(shí)攝像機(jī)的視頻流(最多6個) 被匯聚在一起逐幀處理,進(jìn)行失真和其他圖像偽影校正,調(diào)整曝光和白平衡,然后動態(tài)拼接成一個360°全景視圖,以4K清晰度和60 fps幀頻輸出,最終投影到一個球形坐標(biāo)空間上。

目前用于此類應(yīng)用的高分辨率魚眼相機(jī)鏡頭通常具有一個廣角視域(FOV)。環(huán)視相機(jī)系統(tǒng)最大的瓶頸之一是: 實(shí)時(shí)到或從外部存儲器存儲/讀取和訪問多路攝像機(jī)輸入數(shù)據(jù),然后將其作為一個單一幀進(jìn)行處理。硬件需要在一幀延遲內(nèi),在輸入攝像機(jī)傳入的原始傳感器數(shù)據(jù)和拼接輸出視頻之間完成處理運(yùn)行。

高性能計(jì)算平臺一直朝著與CPU一起協(xié)同使用FPGA的方向發(fā)展,以便為實(shí)時(shí)圖像處理任務(wù)提供專門的硬件加速。 這種配置使得CPU能專注于特別復(fù)雜的算法,其中它們可以快速切換線程和上下文,并將重復(fù)性任務(wù)分配給一個FPGA,以充當(dāng)可配置的硬件加速器/協(xié)處理器/卸載引擎。 即使將FPGA和CPU作為分立器件使用,系統(tǒng)也可以提高整體效率,因?yàn)檫@些技術(shù)不會發(fā)生沖突,而是像將手套戴在手上一樣來配合在一起。

例如,從魚眼鏡頭獲得的圖像遭受嚴(yán)重失真之苦,因而基于多個相機(jī)視頻生成的拼接操作是高度計(jì)算密集型的任務(wù),其原因?yàn)樗屈c(diǎn)像素操作。這種拼接需要大量的實(shí)時(shí)圖像處理和高度并行化的架構(gòu)。但是,這種下一代的應(yīng)用超過了FPGA可不斷接續(xù)實(shí)現(xiàn)的性能,主要是由于芯片吞吐數(shù)據(jù)的延遲。這反過來會影響整個系統(tǒng)的整體延遲、吞吐速度和性能。

在一個SoC中加入可與CPU一起嵌入的eFPGA半導(dǎo)體知識產(chǎn)權(quán)(IP)。與一個獨(dú)立的FPGA芯片加CPU解決方案相比,嵌入式FPGA陣列結(jié)構(gòu)具有獨(dú)特的優(yōu)勢,主要優(yōu)勢在于性能更強(qiáng)。一個eFPGA可通過一個寬的并行接口直接連接到ASIC(無I / O緩沖器)上,提供顯著提高的吞吐量,以及以個位數(shù)時(shí)鐘周期來計(jì)數(shù)的延遲。低延遲是復(fù)雜的圖像實(shí)時(shí)處理過程的關(guān)鍵,例如糾正魚眼鏡頭的失真這樣的處理。

利用Speedcore eFPGA IP,客戶可以定義其邏輯、內(nèi)存和DSP資源需求,然后Achronix可配置其IP以滿足他們的需求。查找表(LUTs)、RAM單元塊和DSP64單元塊可以像積木一樣進(jìn)行組合,為任何給定的應(yīng)用創(chuàng)建最佳的可編程結(jié)構(gòu)。 除了標(biāo)準(zhǔn)邏輯、嵌入式存儲器和DSP單元模塊之外,客戶還可以在Speedcore eFPGA結(jié)構(gòu)里面定義他們自己的功能塊。通過把這些定制功能模塊與傳統(tǒng)構(gòu)建模塊一起集成到邏輯陣列結(jié)構(gòu)中,可添加優(yōu)化過的功能來減少面積和提高目標(biāo)應(yīng)用的性能,可使eFPGA的性能得到極大的提高,特別是對嵌入式視覺和圖像處理算法非常有效。

用自定義單元塊來成功地解決高性能圖像處理就是一個很好的例子,在實(shí)現(xiàn)您只看一次(YOLO)這一種使用了神經(jīng)網(wǎng)絡(luò)的、最先進(jìn)的、實(shí)時(shí)對象檢測算法時(shí),可以優(yōu)于早期的方法大大提高性能。該算法依賴于大量的矩陣乘法器,而在FPGA中實(shí)現(xiàn)時(shí),這些矩陣乘法器需要使用DSP和RAM模塊來構(gòu)建;YOLO所需要的DSP和RAM模塊之間的最佳配置,與一個典型的FPGA陣列結(jié)構(gòu)中發(fā)現(xiàn)的不匹配之處就會出現(xiàn)問題。例如,F(xiàn)PGA陣列結(jié)構(gòu)可能提供18×27乘法/累加單元塊和32×128 RAM的DSP單元塊,而此時(shí)的最佳解決方案可能是帶有48×1024 RAM的16×8 DSP單元塊。通過創(chuàng)建實(shí)現(xiàn)最佳DSP和RAM模塊配置的定制單元塊,所得到的Speedcore陣列結(jié)構(gòu)所使用的芯片面積就會減少40%,來實(shí)現(xiàn)相同的功能并且能獲得更高級別的系統(tǒng)性能。

在SoC中嵌入FPGA陣列結(jié)構(gòu)提供了兩個額外的系統(tǒng)級好處:

更低的功耗 - 可編程I / O電路占獨(dú)立FPGA芯片總功耗的一半,而一個eFPGA可以與主控SoC中的其他模塊直接內(nèi)部線路連接,完全不需要大型可編程I / O緩沖器。

更低的系統(tǒng)成本 - 由于eFPGA只需實(shí)現(xiàn)特定功能,eFPGA的裸片尺寸遠(yuǎn)小于等效的獨(dú)立FPGA芯片,這是因?yàn)閑FPGA不再需要可編程的I / O緩沖器和不必要的接口邏輯。

借助超低延遲和實(shí)時(shí)處理功能,可以有效實(shí)現(xiàn)基于360°視域的視覺系統(tǒng),具有定制單元塊的Speedcore eFPGA與同一主控SoC中的一個CPU配合使用,非常適合去實(shí)現(xiàn)專用功能,如目標(biāo)檢測和圖像識別、變形和失真校正、以及最后將最終圖像拼接在一起。在SoC中嵌入FPGA陣列結(jié)構(gòu)是超深亞微米時(shí)代系統(tǒng)集成的一個自然發(fā)展過程。

推薦閱讀: