【導(dǎo)讀】未來幾年,汽車的安全系統(tǒng)將會變得更加復(fù)雜。推動該趨勢的一個主要動力是預(yù)期的監(jiān)管措施,它們將對汽車安全氣囊和穩(wěn)定控制系統(tǒng)的配售率和成熟度產(chǎn)生影響。本文探討在這些系統(tǒng)中使用F-RAM非易失性存儲技術(shù)的主要技術(shù)優(yōu)勢。

鐵電RAM(F-RAM)存儲器被用在一系列廣泛的應(yīng)用中,其中包括工業(yè)控制系統(tǒng)、工業(yè)自動化、任務(wù)關(guān)鍵型應(yīng)用和汽車系統(tǒng)等。未來幾年,汽車的安全系統(tǒng)將會變得更加復(fù)雜。推動該趨勢的一個主要動力是預(yù)期的監(jiān)管措施,它們將對汽車安全氣囊和穩(wěn)定控制系統(tǒng)的配售率和成熟度產(chǎn)生影響。本文探討在這些系統(tǒng)中使用F-RAM非易失性存儲技術(shù)的主要技術(shù)優(yōu)勢。

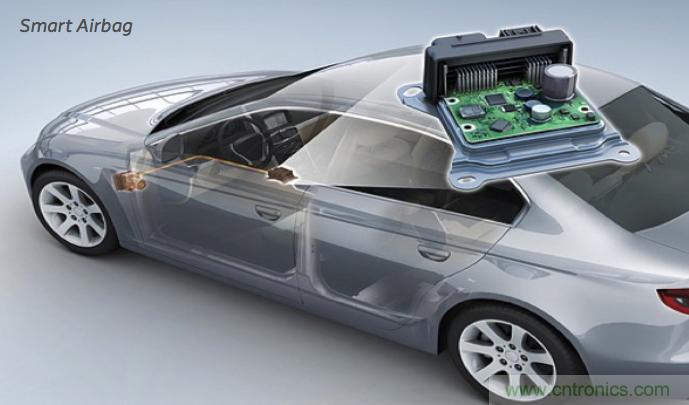

“安全氣囊系統(tǒng)”正在發(fā)生兩大變化。首先,所有新型安全氣囊都配有一個智能傳感器,用于檢測車內(nèi)是否有乘客。安全氣囊的每一次誤彈出都會導(dǎo)致極高的更換成本以及相應(yīng)的維護、人工和部件成本。能夠持續(xù)監(jiān)測乘客的重量和存在的智能傳感器能夠為安全氣囊的運行增加一個“可變性”,從而既能避免安全氣囊誤觸發(fā)對乘客造成傷害,也能在嚴(yán)重碰撞時為乘客提供保護。

其次,“安全氣囊系統(tǒng)”在事故發(fā)生之前將“實際信息或數(shù)據(jù)”采集到行車記錄儀(EDR)里。這對于今后的訴訟或保險索賠有很大的價值。EDR功能通常內(nèi)置于安全氣囊電子控制單元(ECU)中。這是一種自然組合,因為EDR并不需要像飛機黑匣子那么高的耐受性要求,而且安全氣囊控制器是接收各類重要傳感器輸入的主要器件,此外,汽車上沒有安裝獨立EDR的空間。

這兩個要求導(dǎo)致我們需要一個可讀寫次數(shù)極高、存取速度較快的非易失性存儲器。對于“智能”安全氣囊而言,設(shè)計人員希望部署碰撞時彈力可變的安全氣囊。對存儲的要求是:頻繁記錄座位位置以及乘客的重量和存在/實際位置。在維護歷史方面,存儲器有足夠的空間來存儲最后15–20秒的信息。由于一輛普通汽車通常能夠運行30多年,這個存儲器應(yīng)具備較快的寫速度、即時非易失性和極高的可讀寫次數(shù)。

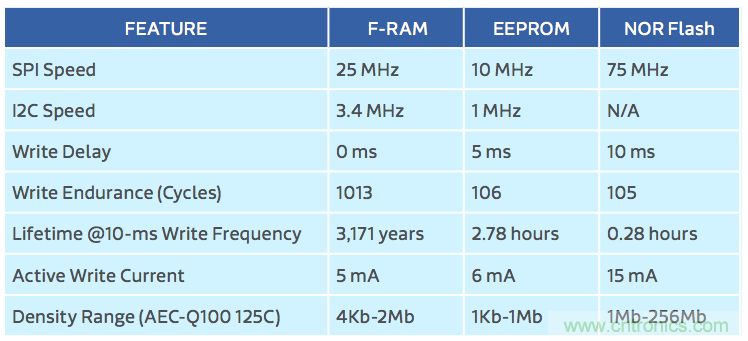

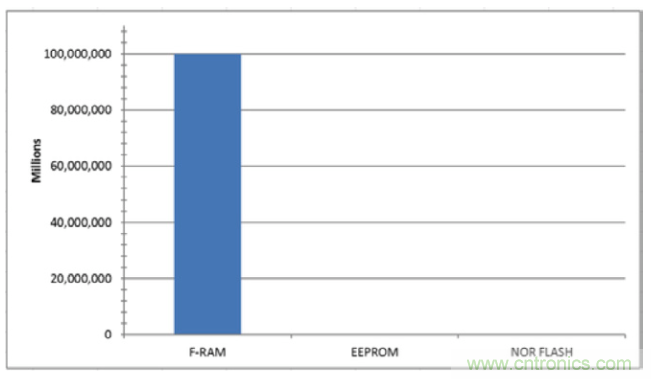

F-RAM是一種非常適合這些要求的存儲器技術(shù)。與其它技術(shù)一樣,它也提供非易失性存儲功能。F-RAM的主要優(yōu)勢是極高的可寫次數(shù)和寫速度。有了F-RAM,系統(tǒng)將能以全總線速度持續(xù)存儲數(shù)據(jù),而且無需額外的存儲器、開銷或損耗均衡等技術(shù)來管理存儲器的可讀寫次數(shù)。這是因為F-RAM具備即時非易失性特點,無需額外準(zhǔn)備時間 即可存儲信息。其可寫次數(shù)高達1014量級。與此相比,大多數(shù)EEPROM和閃存的可惜次數(shù)還不足 106。

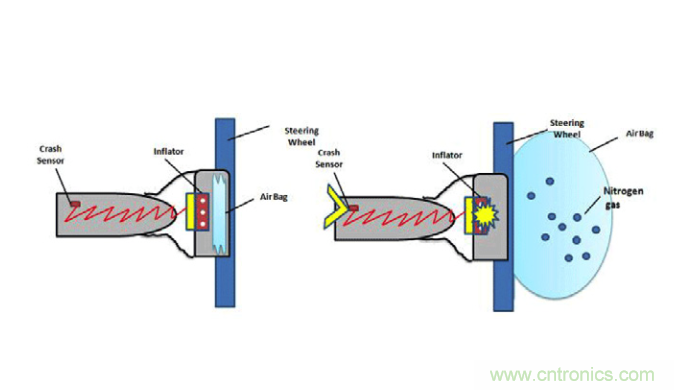

安全氣囊設(shè)計

圖一:安全氣囊設(shè)計

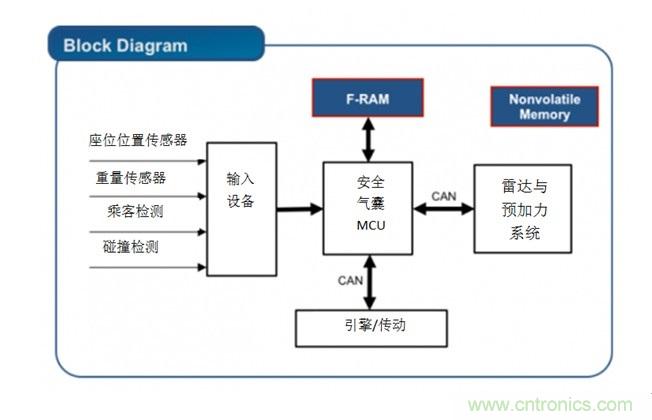

鑒于安全性和極高的更換成本,汽車制造商增添了各類用于記錄乘客位置的傳感器,其中包括用于啟動安全氣囊子系統(tǒng)的乘客壓力傳感器,和一系列用于提升安全氣囊系統(tǒng)有效性的位置傳感器。位置數(shù)據(jù)需要頻繁更新,而且必須存儲到點,甚至是系統(tǒng)部署時刻。將位置數(shù)據(jù)持續(xù)記錄和存儲到一個非易失性存儲器之中的要求使得高性能、低功耗、高讀寫次數(shù)的F-RAM成為一個理想選擇。

圖二:高級非易失性存儲器對比

相比浮柵技術(shù)的優(yōu)勢

圖三:安全氣囊系統(tǒng)的典型框圖

隨著汽車設(shè)計要求的復(fù)雜性不斷增高,浮柵技術(shù)的局限性變得日益明顯。例如,浮柵存儲的編程過程需要數(shù)微秒,這對于安全關(guān)鍵型應(yīng)用而言是一段很長的時間。如果碰撞時突然發(fā)生停電,那么只有很少的信息能夠存儲在浮柵存儲器中。

編程過程也會損壞絕緣層,因此,這類存儲器的可寫次數(shù)很有限,僅為100,000到1,000,000次。例如在客載傳感器中,數(shù)據(jù)更新量遠遠高于這個極限。假設(shè)典型的要求是數(shù)據(jù)每一秒更新一次,浮柵存儲器不到12天就會損耗殆盡。斷電時將數(shù)據(jù)緩存到RAM中并寫入浮柵存儲器,就會給EDR帶來數(shù)據(jù)速度問題,因此不可行。

在智能安全氣囊系統(tǒng)中,不僅需要在碰撞時存儲數(shù)據(jù),而且最好能夠存儲事故發(fā)生前的數(shù)據(jù)。理想的解決方案是使用一個滾動日志存儲碰撞前數(shù)據(jù),但實踐證明這種方法不適用于浮柵存儲器,因為它們的可寫次數(shù)有限。由于安全氣囊模塊配有大電容器,而它們存儲有充足的電能來啟動安全氣囊的電能,因此,碰撞發(fā)生后可能仍有殘余電能足夠支持從緩沖器寫入數(shù)據(jù)。但其所能寫入的數(shù)據(jù)量和存儲寫入速度取決于可用的電量。一個典型的2K字節(jié)的浮柵存儲器每5ms約可寫入4字節(jié),因此,寫滿整個浮柵存儲器可能需要一秒以上時間。

圖四:非易失性數(shù)據(jù)緩沖器

賽普拉斯F-RAM的可寫次數(shù) Vs EEPROM和閃存的可寫次數(shù)

由于擁有極高的可寫次數(shù),F(xiàn)-RAM可被用作數(shù)據(jù)緩沖器。MCU可在運行時將事件持續(xù)直接寫入 F-RAM。由于F-RAM是一種固有的非易失性存儲器,它可以在斷電后保存數(shù)據(jù)。因此,即使主電源被切斷,最后一刻的數(shù)據(jù)也不會遭到損壞。由于數(shù)據(jù)是被直接寫入F-RAM的,因此不需要將最后一刻的數(shù)據(jù)從SRAM傳送到EEPROM或閃存等非易失性存儲空間。F-RAM不需要系統(tǒng)備用電源來保留最后一刻的碰撞數(shù)據(jù)。

無寫時延

為了捕獲全部細節(jié),一些事件需要每秒被記錄100到 1000次。這給現(xiàn)有基于EEPROM或閃存的記錄器帶來了挑戰(zhàn)。EEPROM采用逐頁方式存儲數(shù)據(jù),在將兩頁寫入EEPROM之間需要數(shù)微秒的存儲時延,從而限制了數(shù)據(jù)記錄能力。“無延時”寫入F-RAM可讓系統(tǒng)設(shè)計人員以系統(tǒng)總線速度捕獲和寫入實時數(shù)據(jù)。

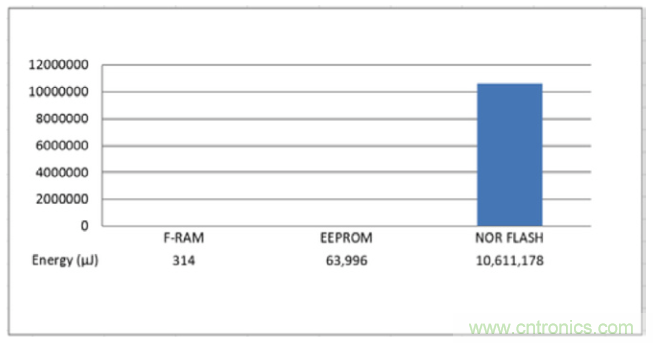

快速寫入和低功耗

圖五:賽普拉斯F-RAM的寫功耗 vs EEPROM和閃存的寫功耗

憑借同類最佳的非易失性寫速度,F(xiàn)-RAM中的高速串行SPI及I2C接口和/或高速并行存取讓控制器能夠?qū)?shù)據(jù)更快地寫入F-RAM。此外,低功耗F-RAM 只需其它非易失性存儲技術(shù)所需總功耗的很小一部分。

高可靠性

EDR的數(shù)據(jù)可靠性對于實現(xiàn)準(zhǔn)確性、耐受性、數(shù)據(jù)檢索以及關(guān)鍵的耐用性目標(biāo)來說非常重要。由于這種存儲空間被用于存儲重要的傳感器數(shù)據(jù),高可靠性和數(shù)據(jù)完整性對于汽車應(yīng)用而言是不可或缺的。

圖六:EDR的數(shù)據(jù)可靠性對于實現(xiàn)準(zhǔn)確性、耐受性、數(shù)據(jù)檢索和關(guān)鍵的耐用性來說非常重要

成熟度

與其它類型的應(yīng)用相比,汽車市場更加關(guān)注技術(shù)成熟度。EEPROM和閃存技術(shù)已為人熟知,主要供應(yīng)商都擁有成熟的質(zhì)量控制體系。因為技術(shù)界對一項技術(shù)的可靠性和可用性必須了如指掌,引入新技術(shù)自然會讓人猶豫不決。F-RAM在汽車環(huán)境(包括達到125°C極端溫度的引擎蓋內(nèi)應(yīng)用)中出貨量已經(jīng)達到5億多件,可以說其已經(jīng)成熟到了足以讓汽車客戶高枕無憂的程度。

與閃存、EEPROM、電池供電型SRAM和其它類似技術(shù)相比,F(xiàn)-RAM可降低系統(tǒng)成本,提升系統(tǒng)效率,降低復(fù)雜性,并大幅降低功耗。

文章來源于電子技術(shù)設(shè)計。

推薦閱讀: