【導(dǎo)讀】本篇文章主要對目前MOS封裝當(dāng)中存在的一些限制進(jìn)行了介紹,并提出了改善的必要性。在最后,還給出了提高總體能效的方法。希望大家在閱讀過本篇文章之后,能對MOS管的封裝有進(jìn)一步的了解。

MOS管是半導(dǎo)體場效應(yīng)管的簡稱。和MOS管相關(guān)的,大多數(shù)是與封裝有關(guān)的問題。在一些條件相同的條件下,目前主流的幾種封裝其實(shí)是存在著一定的限制的。那么這些限制都有哪些,由如何尋找出突破呢?

目前幾種主流的封裝中存在著如下幾種限制:

封裝電感

內(nèi)部焊線框架內(nèi)的漏極、源極和柵極連接處會(huì)產(chǎn)生寄生電感。而源漏極電感將會(huì)以共源電感形式出現(xiàn)在電路中,將會(huì)影響MOSFET的開關(guān)速度。

封裝電阻

MOSFET在導(dǎo)通時(shí)電阻即Rdson,這個(gè)電阻主要包括芯片內(nèi)電阻和封裝電阻。其中焊線等引入的封裝電阻會(huì)因焊線數(shù)量的不同而有很大不同。

PN結(jié)到PCB的熱阻

源極的熱傳導(dǎo)路徑:芯片>焊線>外部引腳>PCB板,較長的熱傳導(dǎo)路徑必然引起高熱阻,且焊線較細(xì)較長,封裝熱阻會(huì)更高。

PN結(jié)到外殼的熱阻

例如,標(biāo)準(zhǔn)的SO-8器件是塑封材料完全包封,由于塑料是熱的不良導(dǎo)體,芯片到封裝外殼的熱傳導(dǎo)很差。

改善的必要性

下面我們用例子說明一下改善這幾方面的必要性。

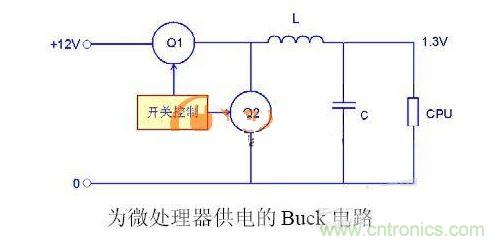

圖1

微處理器供電為例子,這是一個(gè)較為典型的BUCK同步整流的例子。簡單分析可知。現(xiàn)時(shí)CPU的工作頻率已經(jīng)由MHz級(jí)轉(zhuǎn)向GHz 級(jí),工作電壓為1.3V 左右。要求到供電電源上到MHz級(jí)電磁干擾在可控范圍,輸出電流0A~50A(考慮到筆記本電腦或平板電腦從“睡眠”到“大運(yùn)算工作”,正常工作電流10A~20A)。其典型輸入電壓為7.5V 到21V,電路中控制和續(xù)流用的功率器件普遍采用30V 的MOSFET。如圖1所示。

此類電源系統(tǒng)的總體能效一般會(huì)要求在95%以上。

[page]

如何提高總體能效?

要提高總體能效,我們要先對損耗產(chǎn)生機(jī)理進(jìn)行分析。在此BUCK 同步整流電路中存在著多種功率損耗,這里主要考慮的損耗為開關(guān)管(Q1)和續(xù)流管(SR 同步整流管、Q2)的損耗。

從SR-BUCK 電路的工作原理可知:

Q1開通時(shí),Q1存在著導(dǎo)通損耗、驅(qū)動(dòng)損耗;

Q1關(guān)斷時(shí),有輸出電容帶來的損耗;

而Q2在工作區(qū)間除了導(dǎo)通損耗、驅(qū)動(dòng)損耗、開關(guān)損耗、還有體內(nèi)二極管損耗問題。

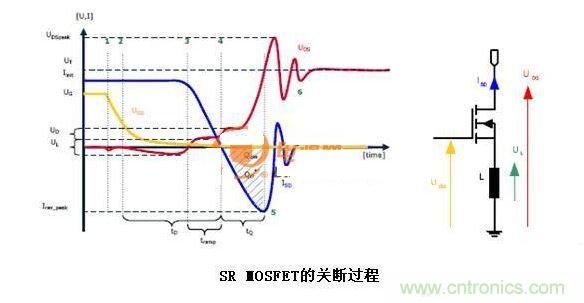

借IR的實(shí)驗(yàn)圖方便分析:

圖2

其中:Td 續(xù)流電流流向體二極管時(shí)間段;

Tramp Vds因漏極電感產(chǎn)生正向壓降;

Tq 積聚Coss與Qrr電荷時(shí)間段;

我們把這些損耗分為三部分,它們和電路、器件的相關(guān)性如下:

導(dǎo)通損耗

與MOSFET的 Rdson相關(guān)。這容易理解,且隨著輸出電流的提高,Rdson損耗也會(huì)相應(yīng)地增加;

與體二極管的正向電壓Vsd相關(guān)。死區(qū)時(shí)間時(shí),續(xù)流電流不得不從MOSFET溝道轉(zhuǎn)而流向體二極管,并由此產(chǎn)生額外的體二極管損耗。體二極管的導(dǎo)通時(shí)間很短,僅為50ns至100 ns左右,因而,這損耗經(jīng)常忽略不計(jì)。但是,當(dāng)輸出電壓和體二極管Vsd相近時(shí),這損耗就不能忽略了。

柵極驅(qū)動(dòng)損耗

取決于MOSFET的Qg。這也容易理解,MOSFET開啟時(shí),必須對柵極進(jìn)行充電,柵極積聚總電荷量為Qg后MOSFET飽和導(dǎo)通。MOSFET關(guān)斷時(shí),則必須將柵極中的電荷放電至源極,這就意味著Qg將消散在柵極電阻和柵極驅(qū)動(dòng)器中。

Qg與Rdson非線形反比。即并聯(lián)多個(gè)MOSFET降低Rdson 而降低導(dǎo)通損耗時(shí),因Qg增大令驅(qū)動(dòng)損耗會(huì)相應(yīng)增大。

[page]

Coss損耗

與MOSFET的輸出電容Coss相關(guān)。

Q2關(guān)斷時(shí),必須將輸出電容充電至線電壓,因此,在關(guān)斷過程中產(chǎn)生的感應(yīng)電量直接取決于MOSFET的Coss,且這些電量通過寄生電感、寄生電阻釋放時(shí)將觸發(fā)LC振蕩,并會(huì)由此對Q2的Vds產(chǎn)生電壓尖峰。

與MOSFET的反向恢復(fù)電荷Qrr有關(guān)

MOSFET關(guān)斷時(shí),必須將Qrr移走,這部分電量會(huì)加入到上面的LC振蕩里。對一些專門為同步整流這方面設(shè)計(jì)的MOSFET器件來說,Qrr可以忽略不計(jì),因?yàn)槠鋵偣牡挠绊懳⒑跗湮ⅰ?/div>

封裝電阻的局限

按上面的分類,容易看出,當(dāng)輸出電流小時(shí),導(dǎo)通損耗相對小;輸出電流大,導(dǎo)通損耗也相對大。而開關(guān)損耗(驅(qū)動(dòng)損耗+輸出電容損耗)變化不大。(想一下,筆記本電腦從“睡眠”到“正常工作”,工作電流范圍:0A~20A。)

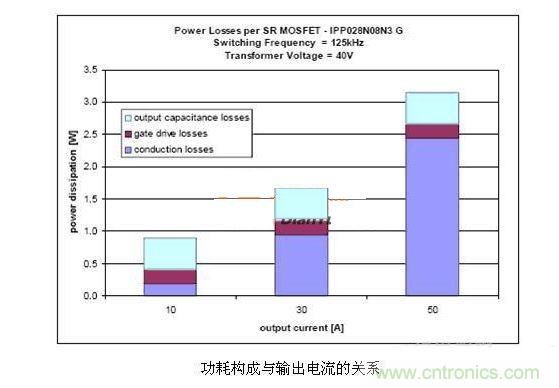

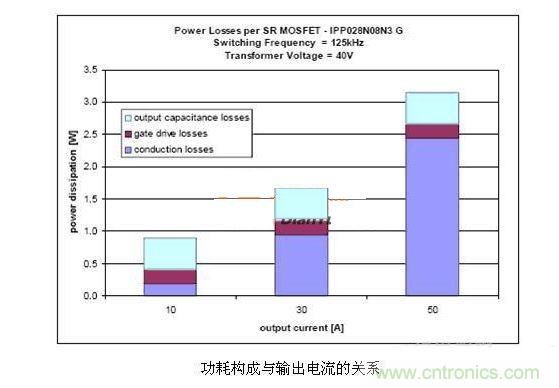

而三種損耗相對變化的幅度比例,我們再借IR的實(shí)測圖例來說明。

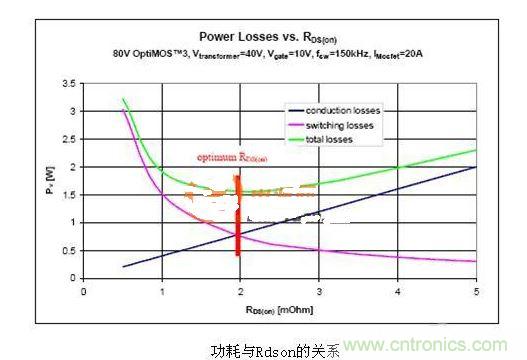

圖3

可看出,在輕負(fù)載條件下,導(dǎo)通損耗占總功耗的比例極低。在這種情況下,在整個(gè)負(fù)載范圍內(nèi)基本保持不變的開關(guān)損耗是主要損耗。但是,當(dāng)輸出電流較高時(shí),導(dǎo)通損耗則成為最主要的損耗,其占總功耗的比例也最高。

因此,要優(yōu)化SR MOSFET的效率,必須找到開關(guān)損耗與導(dǎo)通損耗之間的最佳平衡點(diǎn)。

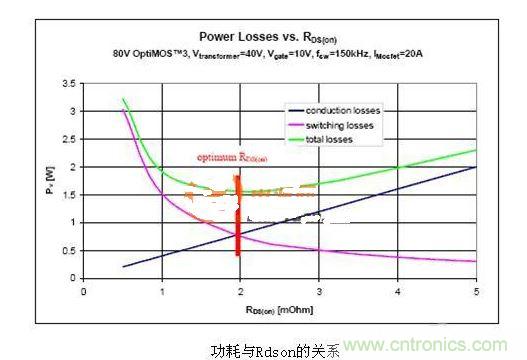

圖4

如圖4所示。當(dāng)Rdson超出最優(yōu)值時(shí),總功耗將隨Rdson的提高而線性增加。但當(dāng)Rdson降至低于最優(yōu)值時(shí),總功耗也會(huì)因輸出電容的快速增加而急劇上升。如圖在1毫歐以下時(shí),Rdson僅下降0.5毫歐姆,便會(huì)令總功耗提高一倍,從而嚴(yán)重降低電源轉(zhuǎn)換器的效率。

說到這里,我們回過頭,看看上面說到的焊線式封裝在封裝電阻和封裝電感兩方面的局限。

[page]

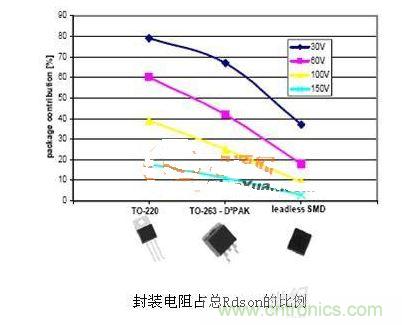

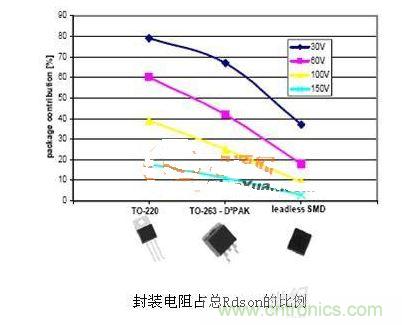

封裝電阻的局限

以現(xiàn)在使用到的30V同步整流SR MOSFET,可達(dá)1~2毫歐姆的的導(dǎo)通電阻,而TO220的封裝電阻在1毫歐姆左右,這樣封裝電阻占總Rdson的比例高達(dá)50%以上。在耐壓高一些的MOSFET中(耐壓高,Rdson相對高),這個(gè)比例會(huì)相對低一些。但和無引腳的SMD封裝MOSFET比較,還是有一定差距的??聪旅姹容^圖:

圖5

對同一工藝的MOS芯片,Rdson*Qg是相對固定值。選擇封裝電阻更低的封裝形式,在低Rdson下,追求更低的Qg,更低的Coss,提供更多的選擇。

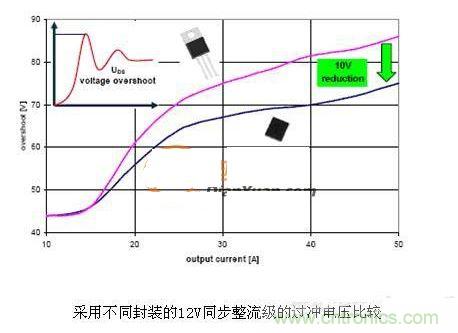

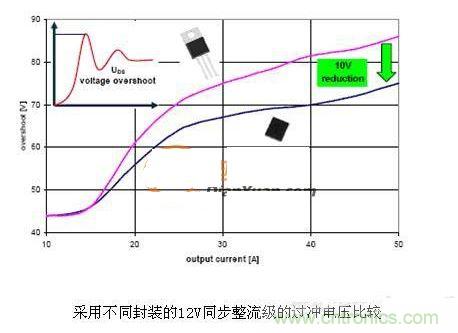

封裝電感的局限

上面提到,SR MOSFET關(guān)斷時(shí),Coss和Qrr的電荷通過寄生電感、寄生電阻釋放時(shí)將觸發(fā)LC振蕩,這樣會(huì)造成一個(gè)過沖高壓。因此需要盡量減少寄生電感。

圖6

如TO220封裝的寄生電感為10nH左右,甚至更高。無引腳SMD封裝,得益于其無引腳設(shè)計(jì)以及所采用的銅帶或夾焊技術(shù),寄生電感可大大降低至0.2nH左右。以12V同步整流級(jí)為例,只要用低電感封裝來取代TO220封裝,就能將過沖電壓降低10V,參見圖6。

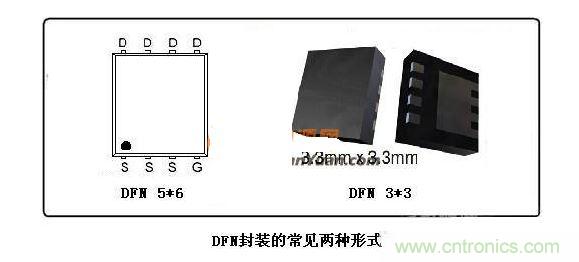

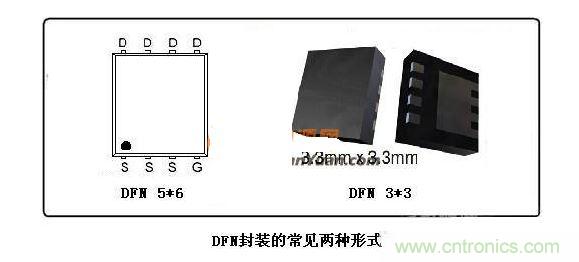

當(dāng)電壓應(yīng)力較小時(shí),可以使用電壓值更低的MOSFET,以進(jìn)一步優(yōu)化系統(tǒng)的總體性能。上面說到的“無引腳SMD封裝”,現(xiàn)在市場上常見到的,如:DFN封裝(各廠家有不同命名)。

DFN封裝,是在SO-8的基礎(chǔ)上,對焊線互連形式進(jìn)行改進(jìn),用金屬帶、或金屬夾板代替焊線,降低封裝電阻、封裝電感,并且改善了熱阻。DFN封裝的MOSFET,在低壓同步整流應(yīng)用上的優(yōu)勢是顯而易見的,各大半導(dǎo)體廠家都專門針對此封裝形式推出了不少器件產(chǎn)品。