【導(dǎo)讀】在硬件系統(tǒng)設(shè)計(jì)中,通常我們關(guān)注的串?dāng)_主要發(fā)生在連接器、芯片封裝和間距比較近的平行走線之間。但在某些設(shè)計(jì)中,高速差分過孔之間也會產(chǎn)生較大的串?dāng)_,本文對高速差分過孔之間的產(chǎn)生串?dāng)_的情況提供了實(shí)例仿真分析和解決方法。

高速差分過孔間的串?dāng)_

對于板厚較厚的PCB來說,板厚有可能達(dá)到2.4mm或者3mm。以3mm的單板為例,此時(shí)一個(gè)通孔在PCB上Z方向的長度可以達(dá)到將近118mil。如果PCB上有0.8mm pitch的BGA的話,BGA器件的扇出過孔間距只有大約31.5mil。

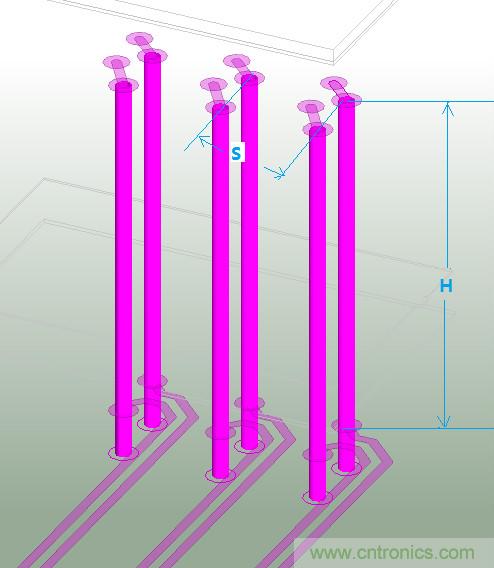

如圖1所示,兩對相鄰差分過孔之間Z方向的并行長度H大于100mil,而兩對差分過孔在水平方向的間距S=31.5mil。在過孔之間Z方向的并行距離遠(yuǎn)大于水平方向的間距時(shí),就要考慮高速信號差分過孔之間的串?dāng)_問題。順便提一下,高速PCB設(shè)計(jì)的時(shí)候應(yīng)該盡可能最小化過孔stub的長度,以減少對信號的影響。如下圖所1示,靠近Bottom層走線這樣Stub會比較短。或者可以采用背鉆的方式。

圖1:高速差分過孔產(chǎn)生串?dāng)_的情況(H>100mil, S=31.5mil )

差分過孔間串?dāng)_的仿真分析

下面是對一個(gè)板厚為3mm,0.8mm BGA扇出過孔pitch為31.5mil,過孔并行距離H=112mil的設(shè)計(jì)實(shí)例進(jìn)行的仿真。

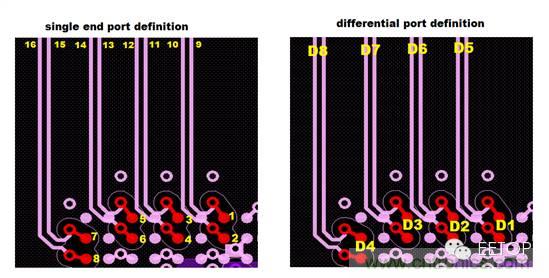

如圖2所示,我們根據(jù)走線將4對差分對定義成8個(gè)差分端口。

圖2:串?dāng)_仿真端口定義

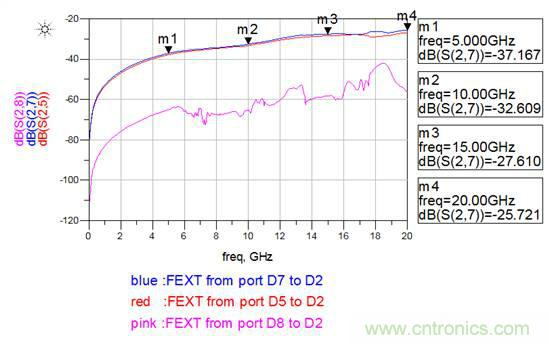

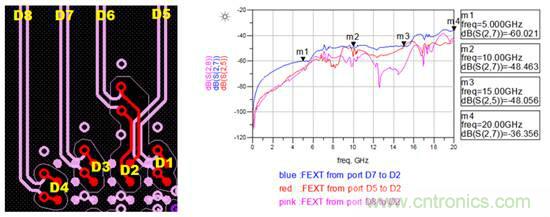

假設(shè)差分端口D1—D4是芯片的接收端,我們通過觀察D5、D7、D8端口對D2端口的遠(yuǎn)端串?dāng)_來分析相鄰?fù)ǖ赖拇當(dāng)_情況。由圖3所示的結(jié)果我們可以看到距離較近的兩個(gè)通道,通道間的遠(yuǎn)端串?dāng)_可以達(dá)到-37dB@5GHz和-32dB@10GHz,需要進(jìn)一步優(yōu)化設(shè)計(jì)來減小串?dāng)_。

圖3:差分對間的串?dāng)_仿真結(jié)果

也許讀到這里您會產(chǎn)生疑問:如何判定是差分過孔引起的串?dāng)_而不是差分走線引起的串?dāng)_呢?

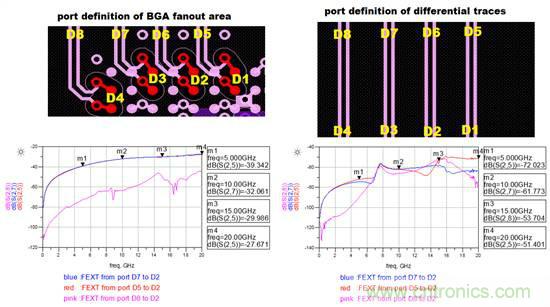

為了說明這個(gè)問題,我們將上述的實(shí)例分成BGA扇出區(qū)域和差分走線兩部分分別進(jìn)行仿真。仿真結(jié)果如圖4所示:

圖4:BGA扇出區(qū)域和差分走線串?dāng)_仿真結(jié)果

從圖4右側(cè)的仿真結(jié)果可以看出差分走線間的串?dāng)_都在-50dB以下,在10GHz頻段下甚至達(dá)到了 -60dB以下。而BGA扇出區(qū)域的串?dāng)_和原來整體仿真的串?dāng)_數(shù)值比較接近。從圖4中的仿真結(jié)果我們可以得出在上述實(shí)例中差分過孔間的串?dāng)_起主要作用。

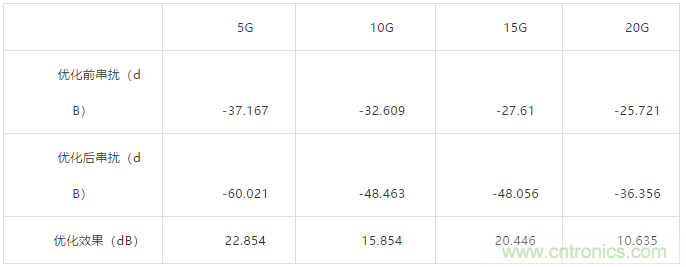

差分過孔間串?dāng)_的優(yōu)化

了解了此類問題產(chǎn)生串?dāng)_的根源,優(yōu)化差分過孔之間串?dāng)_的方法就比較明確了。增加差分過孔之間的間距是簡單易行并且十分有效的方法。我們在實(shí)例原設(shè)計(jì)的基礎(chǔ)上將差分過孔位置進(jìn)行了優(yōu)化,使得每對差分過孔之間的間距大于75mil。從圖5所示的仿真結(jié)果以及表1的數(shù)據(jù)對比可以看出,優(yōu)化后的遠(yuǎn)端串?dāng)_比原設(shè)計(jì)在15GHz頻帶內(nèi)有15~20dB的改善,在15~20GHz頻帶內(nèi)有10dB的改善。

圖5:優(yōu)化差分過孔間距后串?dāng)_仿真結(jié)果

表1:優(yōu)化差分過孔間距前后串?dāng)_仿真數(shù)據(jù)對比

TI公司推出的應(yīng)用于25/28Gbps接口速率的DS280BR810芯片在PCB設(shè)計(jì)上可以使用這種降低串?dāng)_的扇出方法。DS280BR810是一個(gè)8通道28Gbps低功耗線性均衡器。

推薦閱讀:

開關(guān)電源穩(wěn)定性的設(shè)計(jì)與測試!