【導(dǎo)讀】很多人一看到這個(gè)標(biāo)題,相信都會(huì)嘴角一揚(yáng),鄙視地笑了:GPIO和上下拉電阻有什么好談的,不就是一個(gè)電阻接地或者接電源嗎?學(xué)電子的第一堂課就學(xué)了。實(shí)際上,上下拉電阻這里的學(xué)問深著呢,各位要是不信,先用下面幾個(gè)實(shí)例自測一下,再?zèng)Q定要不要學(xué)一下。

入門題:

1)什么是開漏輸出,什么是推挽輸出?

2)芯片空余的引腳如何處理,接地?接電源?懸空?

進(jìn)階題:

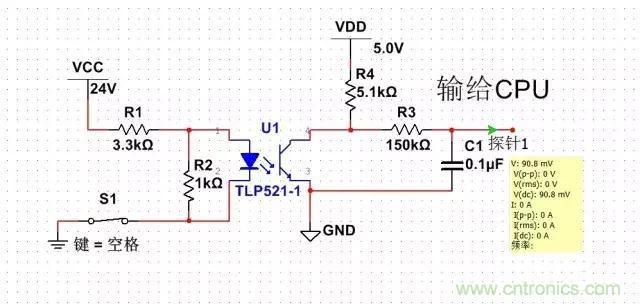

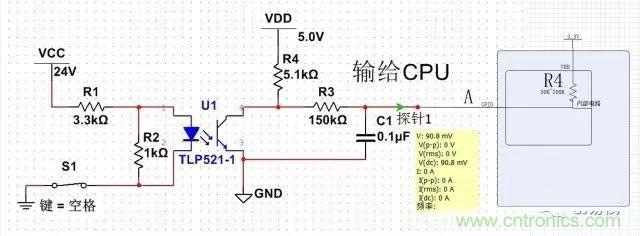

下圖1是PLC的輸入端口原理圖,S1是模擬開關(guān)信號(hào)輸入。軟件工程師說按鍵按下,CPU一直檢測不到低電平,一直都是高電平,一口咬定是硬件問題,實(shí)測CPU的引腳確實(shí)也是3V左右的高電平。請問是軟件問題還是硬件問題,原因是什么?(下圖R3和C1參數(shù)不能改,用于設(shè)置輸入濾波參數(shù),限制頻率高于10HZ的抖動(dòng)輸入。)

PLC產(chǎn)品的輸入端口原理圖

高級(jí)題:

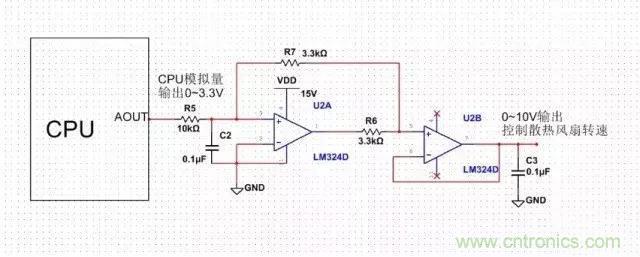

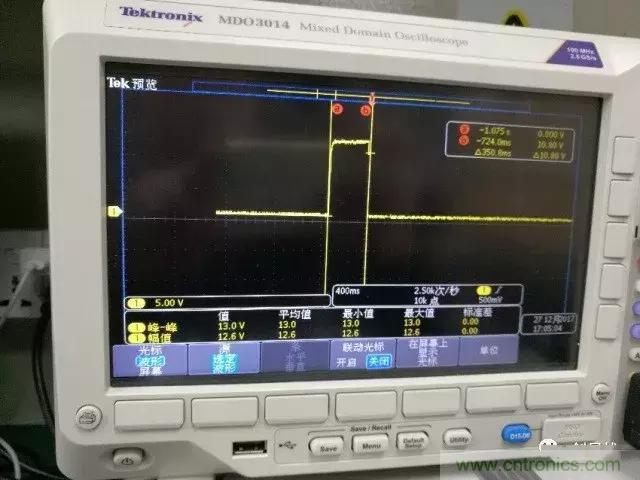

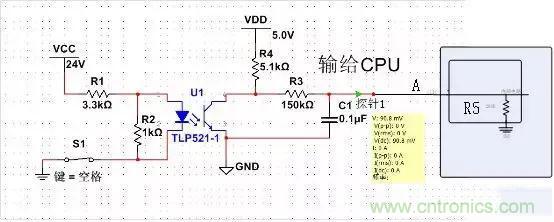

下圖2是控制機(jī)柜風(fēng)扇控制電路,控制器輸出0~10V電壓,控制風(fēng)扇的轉(zhuǎn)速。目前該控制器存在這個(gè)問題:控制一上電,端口處就會(huì)輸出400mS/5V左右的脈沖,導(dǎo)致上電瞬間風(fēng)扇突然轉(zhuǎn)動(dòng),客戶不可接受,需整改。怎么解決?

圖2 :風(fēng)扇轉(zhuǎn)速控制原理圖

圖3 :風(fēng)扇控制上電瞬間400mS左右的高電平輸出

骨灰題:

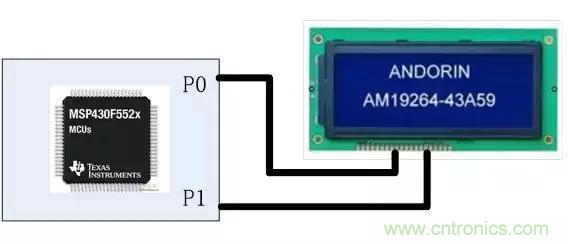

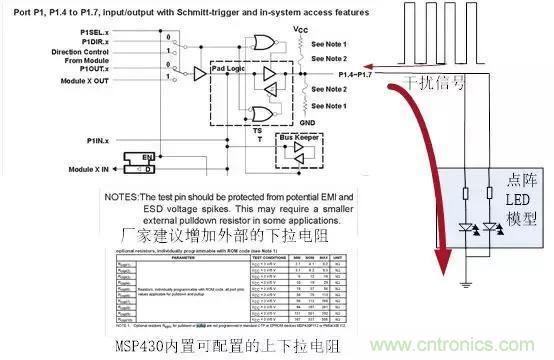

下圖4是一款智能電表的方案示意圖,項(xiàng)目組一共開發(fā)了2款電表,高端版和低端版,主板是完全一樣的,區(qū)別在于高端版帶顯示器,低端版不帶顯示器。兩款設(shè)備在做EMC的ESD測試中,低端版設(shè)備做完實(shí)驗(yàn)后無法啟動(dòng),高端版則正常,請問可能的原因在哪里?

圖4 :帶顯示功能的智能電表

一、GPIO的基礎(chǔ)知識(shí)

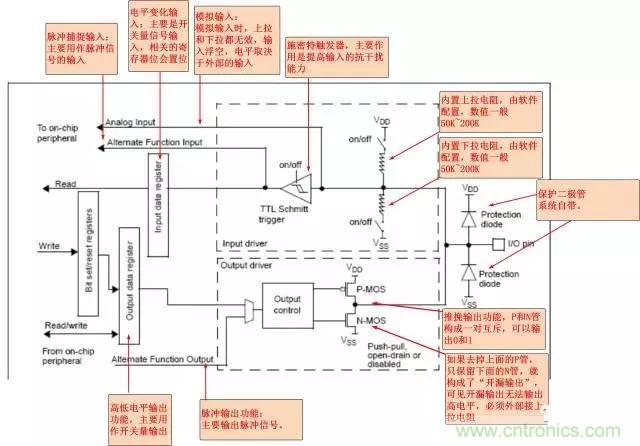

GPIO(General Purpose I/O Ports)意思為通用輸入/輸出端口,通俗地說,就是一些引腳,可以通過它們輸出高低電平或者通過它們讀入引腳的狀態(tài)-是高電平或是低電平。GPIO口一是個(gè)比較重要的概念,用戶可以通過GPIO口和硬件進(jìn)行數(shù)據(jù)交互(如UART),控制硬件工作(如LED、蜂鳴器等),讀取硬件的工作狀態(tài)信號(hào)(如中斷信號(hào))等。幾乎所有的CPU、MCU都會(huì)具GPIO功能,以下是作者統(tǒng)計(jì)的GPIO的種類,幾乎囊括了所有的MCU的GPIO類型。

1) 輸入浮空:即輸入端口既不上拉也不下拉,電平由外部輸入決定;這種模式較少,一般模擬量輸入、按鍵掃描輸入使用該模式。

2) 輸入上拉:即輸入端口配置一個(gè)電阻到電源端,該電阻可以使芯片內(nèi)置,也可以是外部電阻。

3) 輸入下拉:即輸入端口配置一個(gè)電阻到地,該電阻可以使芯片內(nèi)置,也可以是外部電阻。

4) 模擬輸入:模擬量信號(hào)輸入,需要芯片內(nèi)部支持AD轉(zhuǎn)換功能才可以。

5) 開漏輸出: 漏極開路輸出(OD) 和集電極開路輸出(OC)十分相似,都是無法輸出高電平,只能輸出低電平,需要高電平時(shí)需要外接上拉電阻。

6) 推挽式輸出:推挽輸出既可以輸出高電平也可以輸出低電平,無需外配置電阻。

7) 推挽式復(fù)用功能:即推挽式輸出和輸入功能,使用時(shí)需要配置具體使用哪一種。

8) 開漏復(fù)用功能:即開漏輸出和輸入功能,使用時(shí)需要配置具體使用哪一種。

很多人看到上面一堆IO引腳的功能種類,肯定都是云里霧里的。先不急,看完下面這張“葵花寶典”,可以肯定市面上99%的CPU的GPIO功能都囊括了,拿著這張表,硬件工程師可以說服驅(qū)動(dòng)工程師,驅(qū)動(dòng)工程師可以忽悠軟件工程師,就可以責(zé)任清晰,和平共處了。

圖5:8種GPIO輸入輸出功能類型內(nèi)部原理框圖

二、上下拉電阻作用

1) 上拉就是將不確定的信號(hào)通過一個(gè)電阻嵌位在高電平!電阻同時(shí)起限流作用!下拉同理,下拉就是將不確定的信號(hào)通過一個(gè)電阻嵌位在低電平!電阻同時(shí)起限流作用!

2) 上拉是對(duì)器件注入電流,下拉是輸出電流。

3) 弱強(qiáng)只是上拉電阻的阻值不同,沒有什么嚴(yán)格區(qū)分。

4) 對(duì)于非集電極(或漏極)開路輸出型電路(如普通門電路)提升電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開路輸出型電路輸出電流通道。

5) 一般作單鍵觸發(fā)使用時(shí),如果IC本身沒有內(nèi)接電阻,為了使單鍵維持在不被觸發(fā)的狀態(tài)或是觸發(fā)后回到原狀態(tài),必須在IC外部另接一電阻。

6) 數(shù)字電路有三種狀態(tài):高電平、低電平、和高阻狀態(tài),有些應(yīng)用場合不希望出現(xiàn)高阻狀態(tài),可以通過上拉電阻或下拉電阻的方式使處于穩(wěn)定狀態(tài),具體視設(shè)計(jì)要求而定!

7) 一般說的是I/O端口,有的可以設(shè)置,有的不可以設(shè)置,有的是內(nèi)置,有的是需要外接。

8) 上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的,也就是我們通常所說的灌電流。

9) 在I/O引腳懸空時(shí),接電阻就是為了防止輸入端懸空,從而提高系統(tǒng)的抗干擾能力。減弱外部電流對(duì)芯片產(chǎn)生的干擾。

10) 通過上拉或下拉來增加或減小驅(qū)動(dòng)電流。

11) 上下拉電阻改變電平的電位,常用在TTL-CMOS匹配。

12) 上拉電阻可以為OC門或者OD門提供電流。

三、上拉電阻的應(yīng)用場景

1) 當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),若TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平值。注:此時(shí)上拉電阻連接的電壓值應(yīng)不低于CMOS電路的最低高電壓,同時(shí)又要考慮TTL電路方電流(如某端口最大輸入或輸出電流)的影響。

2) OC門或者OD門電路必須加上拉電阻,才能使用。

3) 為加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。

4) 在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻,降低輸入阻抗,提供泄荷通路。

5) 芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力。

6) 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

7) 在數(shù)字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。

四、上拉電阻阻值選擇原則

1) 從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。

2) 從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠?。浑娮栊?,電流大。

3) 對(duì)于高速電路,過大的上拉電阻可能邊沿變平緩。綜合考慮以上三點(diǎn),通常在1k到10k之間選取。對(duì)下拉電阻也有類似道理。

4) 對(duì)上拉電阻和下拉電阻的選擇應(yīng)結(jié)合開關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:

a) 驅(qū)動(dòng)能力與功耗的平衡。以上拉電阻為例,一般地說,上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)是應(yīng)注意兩者之間的均衡。

b) 下級(jí)電路的驅(qū)動(dòng)需求。同樣以上拉電阻為例,當(dāng)輸出高電平時(shí),開關(guān)管斷開,上拉電阻應(yīng)適當(dāng)選擇以能夠向下級(jí)電路提供足夠的電流。

c) 高低電平的設(shè)定。不同電路的高低電平的門檻電平會(huì)有不同,電阻應(yīng)適當(dāng)設(shè)定以確保能輸出正確的電平。以上拉電阻為例,當(dāng)輸出低電平時(shí),開關(guān)管導(dǎo)通,上拉電阻和開關(guān)管導(dǎo)通電阻分壓值應(yīng)確保在零電平門檻之下。

d) 頻率特性。以上拉電阻為例,上拉電阻和開關(guān)管漏源級(jí)之間的電容和下級(jí)電路之間的輸入電容會(huì)形成RC延遲,電阻越大,延遲越大。上拉電阻的設(shè)定應(yīng)考慮電路在這方面的需求。

5) 關(guān)于電阻的參數(shù)不能一概而定,要看電路其他參數(shù)而定,比如通常用在輸入腳上的上拉電阻如果是為了抬高峰峰值,就要參考該引腳的內(nèi)阻來定電阻值的!

6) 一般LED的電流有幾個(gè)mA就夠了,最大不超過20mA,根據(jù)這個(gè)你就應(yīng)該可以算出上拉電阻值來了。

7) 對(duì)于驅(qū)動(dòng)晶體管,又分為PNP和NPN管兩種情況:

a) 對(duì)于NPN:毫無疑問NPN管是高電平有效的,因此上拉電阻的阻值用2K~20K之間的。具體的大小還要看晶體管的集電極接的是什么負(fù)載,對(duì)于LED類負(fù)載,由于發(fā)管電流很小,因此上拉電阻的阻值可以用20k的,但是對(duì)于管子的集電極為繼電器負(fù)載時(shí),由于集電極電流大,因此上拉電阻的阻值最好不要大于4.7K,有時(shí)候甚至用2K的。

b) 對(duì)于PNP管:毫無疑問PNP管是低電平有效的,因此上拉電阻的阻值用100K以上的就行了,且管子的基極必須串接一個(gè)1~10K的電阻,阻值的大小要看管子集電極的負(fù)載是什么,對(duì)于LED類負(fù)載,由于發(fā)光電流很小,因此基極串接的電阻的阻值可以用20k的,但是對(duì)于管子的集電極為繼電器負(fù)載時(shí),由于集電極電流大,因此基極電阻的阻值最好不要大于4.7K。

8) 對(duì)于驅(qū)動(dòng)TTL集成電路,上拉電阻的阻值要用1~10K之間的,有時(shí)候電阻太大的話是拉不起來的,因此用的阻值較小。但是對(duì)于CMOS集成電路,上拉電阻的阻值就可以用的很大,一般不小于20K,通常用100K的。

9) 關(guān)于I2C的上拉電阻:因?yàn)镮2C接口的輸出端是漏極開路或集電極開路,所以必須在接口外接上拉。上拉電阻的取值和I2C總線的頻率有關(guān),工作在standard mode時(shí),其典型值為10K。在FAST mode時(shí),為減少時(shí)鐘上升時(shí)間,滿足上升時(shí)間的要求,一般為1K。電阻的大小對(duì)時(shí)序有一定影響,對(duì)信號(hào)的上升時(shí)間和下降時(shí)間也有影響。總之一般情況下電壓在5V時(shí)選4.7K左右,3.3V在3.3K左右.這樣可加大驅(qū)動(dòng)能力和加速邊沿的翻轉(zhuǎn)

五、GPIO及上下拉電阻實(shí)戰(zhàn)

1、進(jìn)階題:無法輸入低電平問題

我們?nèi)匀灰晕氖椎膯栴}為例,入門題不舉,上述已經(jīng)有答案??催M(jìn)階題。驅(qū)動(dòng)工程師將GPIO的輸入配置成上拉模式(其實(shí)是出廠默認(rèn)模式,驅(qū)動(dòng)工程師不知道要修改。),U1關(guān)閉時(shí),A電電平為高,U1導(dǎo)通時(shí),A點(diǎn)電壓VA=5*R3/(R3+R5)=3V,依然是高電平,所以該配置無法輸入低電平。

圖6 :PLC開關(guān)量輸入上拉配置時(shí)等效電路圖

將GPIO的輸入模式配置成下拉時(shí),U1關(guān)閉時(shí),A點(diǎn)的電壓VA=5*R5/(R3+R4+R5)=電電平為高,U1導(dǎo)通時(shí),A點(diǎn)電壓VA=5*R3/(R3+R5)=2.8V,雖然是屬于高電平的,但是屬于危險(xiǎn)區(qū)域。如果將GPIO配置成懸空模式時(shí),U1關(guān)閉時(shí),A點(diǎn)電壓VA=5V,U1導(dǎo)通時(shí),A點(diǎn)電壓VA≈0.6V,為低電平,功能正確。

圖7:PLC開關(guān)量輸入下拉配置時(shí)實(shí)際等效電路圖

2、高級(jí)題:上電瞬間輸出脈沖問題

經(jīng)過與驅(qū)動(dòng)工程師溝通,他沒有在驅(qū)動(dòng)層配置該引腳為模擬量輸出,該引腳默認(rèn)為輸入,且是內(nèi)置上拉,待cpu跑起來以后,才由應(yīng)用程序配置該引腳為模擬量輸出引腳。導(dǎo)致上電瞬間,程序沒有跑起來,由于內(nèi)置的上拉電阻原因,輸出一個(gè)400ms左右的脈沖。后來在驅(qū)動(dòng)層將該引腳配置為模擬量輸出,并且禁用上拉功能,問題解決。

3、骨灰題的原因級(jí)解決辦法

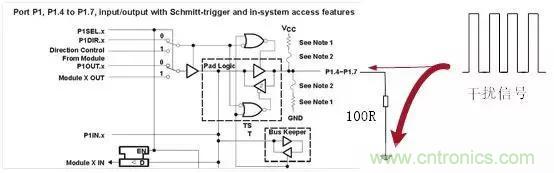

其實(shí)這個(gè)EMC的問題和上下拉電阻又扯上關(guān)系了,如下圖8所示,MSP430內(nèi)部可以配置上拉或者下拉(通過熔絲的方法),阻值也可以配置,但是我們不要忽略一件事情:廠家提供的這些上下拉電阻,只能保證功能性,其上下拉電阻的封裝是相當(dāng)小的,功率是相當(dāng)小的,根本無法提供大能量的釋放通道,不然廠家也不會(huì)建議,為了防止ESD和EMI的破壞,增加外部的較小的下拉電阻。下圖8中,高端版智能電表因?yàn)橥饨恿孙@示屏,顯示屏可以提供大部分的ESD泄放通道,所以沒有損壞到MCU的端口。低端版因?yàn)闆]有顯示器,所有的ESD沖擊都需要通過內(nèi)部電路泄放,內(nèi)部最脆弱的部分就首先被破壞。低端版解決的辦法就如圖9所示,增加外部的低阻抗的電阻到地,絕大部分的能量都通過下拉電阻泄放的地平面上,從而保護(hù)MCU的內(nèi)部電路。

圖8:帶顯示的智能電表等效原理圖

圖9:低阻抗電阻提供一個(gè)干擾信號(hào)的釋放通道

六、后記

GPIO引腳以及上下拉電阻,看似簡單,實(shí)際上幾乎所有的電子行業(yè)從業(yè)人員都吃過這個(gè)虧,包括硬件、驅(qū)動(dòng)、軟件工程師,如果你了解內(nèi)部的原理,犯錯(cuò)的幾率就會(huì)大大降低。希望本文對(duì)你有用。

推薦閱讀: